SiC,全民“挖坑”

有目共睹,SiC功率半導體這幾年的發展速度幾乎超出了所有人意料。其中,由於SiC MOSFET具有取代現有的硅超級結(SJ)晶體管和IGBT技術的潛力,受到了特別關注。

行業老對手和新玩家紛紛湧入,加倍下注這個新興市場。

實際上,SiC MOSFET的發展歷史相當長遠,全球SiC產業龍頭Wolfspeed的前身Cree公司的創始人之一John Palmour早在1987年就申請了一項涉及在SiC襯底上生成MOS電容器的結構,這項專利後來被視爲促成SiC MOSFET誕生的關鍵。

不過,由於襯底良率、制造工藝等問題,直到2010年左右SiC MOSFET才正式實現商業化。

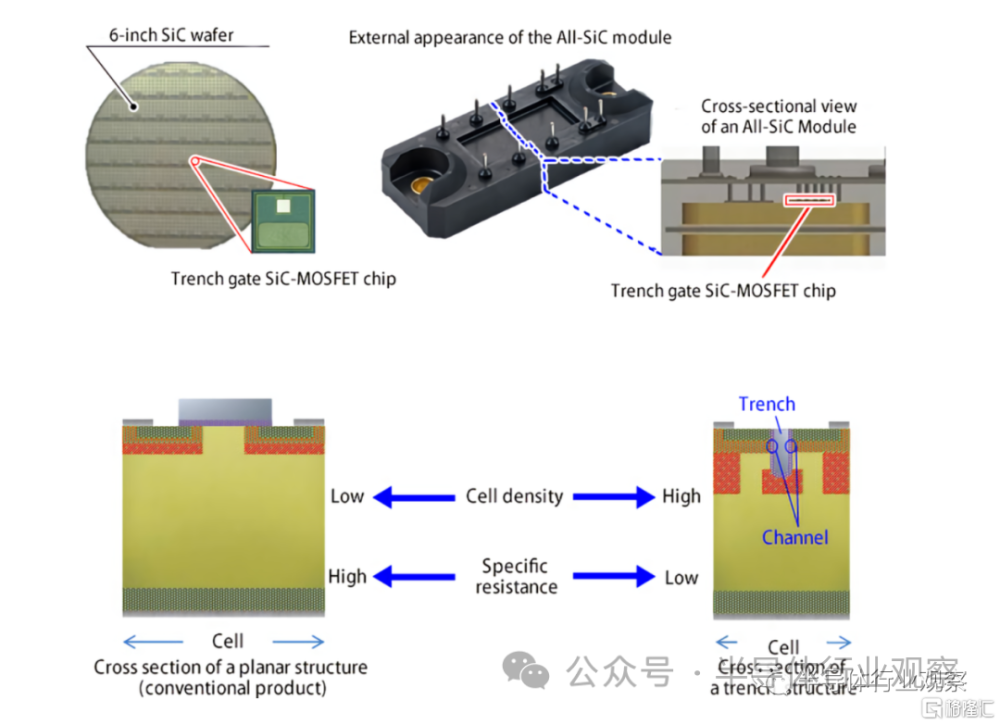

彼時,Cree推出了市場上第一款SiC MOSFET,採用平面柵結構的CMF20120D(另有說法稱,2010年羅姆率先推出了首款平面型SiC MOSFET)。到了2015年,羅姆率先實現溝槽柵結構SiC MOSFET的量產,這種結構更能夠發揮SiC材料的特性,工藝更復雜。

經過近10年的發展,目前在SiC MOSFET的技術路线上,溝槽型SiC MOSFET正在被認爲是更有優勢的技術路线和發展方向。

平面型 or 溝槽型?

在SiC MOSFET的技術路线之爭上,一直有平面柵和溝槽柵兩種不同的結構類型。

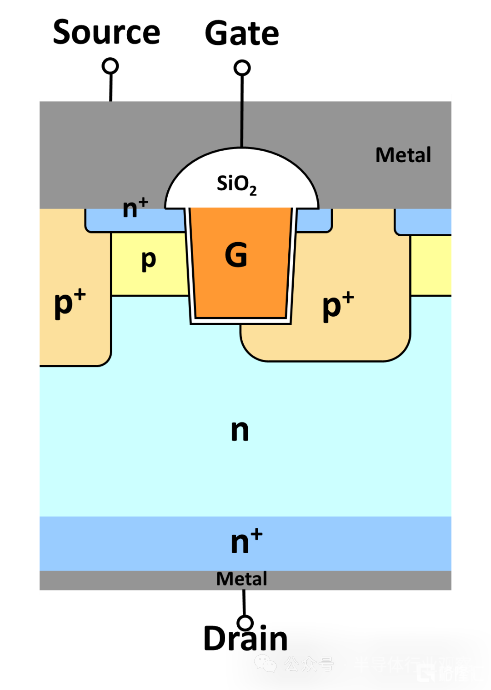

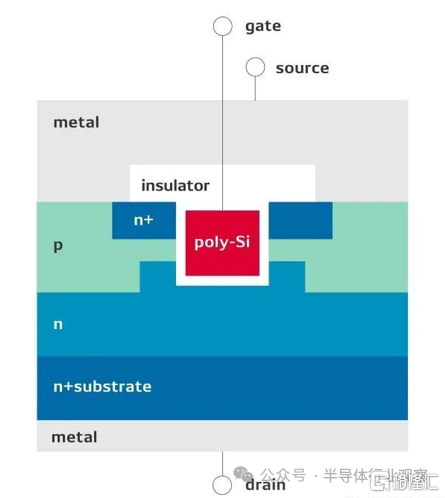

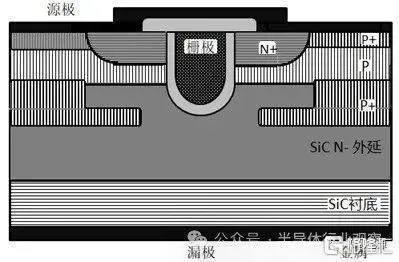

平面柵和溝槽柵都是垂直導電型的MOSFET,兩者在結構上面有相似之處,源極在頂層,漏極在底層,兩者的區別在柵極。

平面柵SiC MOSFET結構:是指柵極電極和源極電極在同一水平面上呈現“平面”分布,溝道與襯底平行。平面柵結構的特點是工藝簡單,單元的一致性較好,雪崩能量比較高。但是,平面柵SiC MOSFET器件由於JFET區的存在,輸入電容較大,從而增加通態電阻,降低了器件的電流能力。

溝槽型SiC MOSFET結構:是指柵極位於源極下方,在半導體材料中形成一個“溝槽”,溝槽柵結構中的溝道和柵極是垂直於襯底的,這也是與平面柵結構的一個顯著區別。盡管其工藝復雜,單元一致性比平面結構差。但是,由於溝槽結構沒有JFET效應,具有更高的溝道密度,同時溝道所在SiC晶面具有較高的溝道遷移率,因此能夠實現更低的比導通電阻,能實現更大電流的導通和更寬的开關速度。

因此,新一代SiC MOSFET主要研究和採用這種結構。

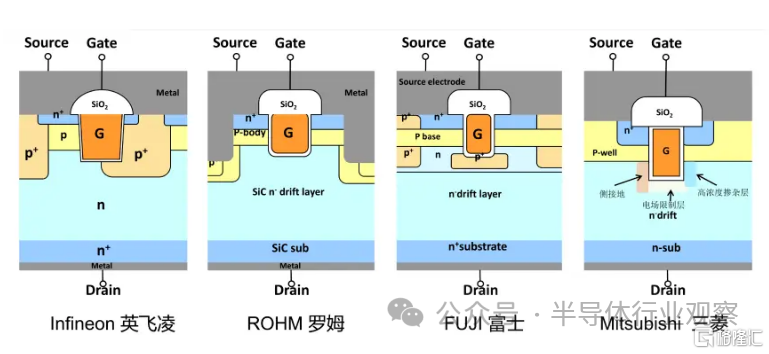

SiC功率MOSFET器件結構

相對而言,平面柵SiC MOSFET工藝復雜度沒那么高,而且开發歷史比較長,國內外相關產品較早實現量產,並且在特拉斯、比亞迪等衆多車企帶動下,平面柵SiC MOSFET功率模塊自2018年就進入了主驅逆變器。

然而,在縮小芯片尺寸,從而提高產量的過程中,平面柵SiC MOSFET的橫向拓撲結構對其最終能夠縮小的程度造成了限制。

相比之下,溝槽型SiC MOSFET器件由於採用了溝槽柵極結構,具有以下突出優點:

導電溝道由橫向改爲縱向,有效節約了器件面積,功率密度大幅提升;

溝槽結構幾乎消除了JFET區,使器件輸入電容大幅減小,提高了开關速度,降低了开關損耗;

JFET區電阻也隨之消除,器件Rdson可以更低電流能力得到進一步提升。

相較平面柵SiC MOSFET器件,溝槽型SiC MOSFET功率密度更大、开關速度更快、導通電阻及損耗更低,因而受到業內企業的高度關注。

通俗的說,溝槽柵SiC MOSFET可以理解爲在平面的基礎上“挖坑”,國際SiC廠商們正在通過溝槽柵來更大的發揮SiC的潛力。不過雖說各家都在“挖坑”,但是方式略微有所不同,放眼望去,有的廠商挖一個坑,有的挖兩個坑,還有的是斜着挖,各種技術結構層出不窮,百花齊放。

業內幾家溝槽柵SiC MOSFET示意圖

爲此,SiC芯片供應商們尤其是國際大廠都在發揮自家各自的本領,开始了對溝槽型SiC MOSFET的探索。

溝槽型SiC MOSFET,多方出擊

在一衆SiC器件頭部供應商中,基本都已經开始向溝槽柵MOSFET進行布局。

羅姆和英飛凌是率先轉向溝槽SiC MOSFET的公司。據Yole報告顯示,溝槽SiC MOSFET陣營目前從原來的羅姆和英飛凌已經擴大到多家頭部大廠,例如住友電工、三菱電機、電裝、Qorvo(UnitedSiC)、ST、Wolfspeed、安森美半導體等等,都在從平面結構的MOSFET向溝槽結構轉型。

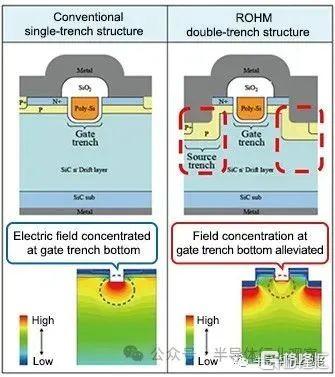

羅姆:雙溝槽結構

2015年,羅姆开發並量產了世界首個溝槽結構的SiC MOSFET,而且是雙溝槽的結構。截止目前,羅姆的溝槽型SiC MOSFET已經發展到了第四代,雙溝槽結構同時具有源極溝槽和柵極溝槽。

羅姆雙溝槽型SiC MOSFET結構

(圖源:羅姆)

在一般的單溝槽結構中,電場集中在柵極溝槽的底部,因此長期可靠性一直是個問題。而羅姆开發的雙溝槽結構,在源區也設置了溝槽結構,緩和了柵極溝槽底部的電場集中,這種結構成功地降低了電場,防止了對柵極溝槽處的氧化層破壞,確保了長期可靠性,提高了器件性能。

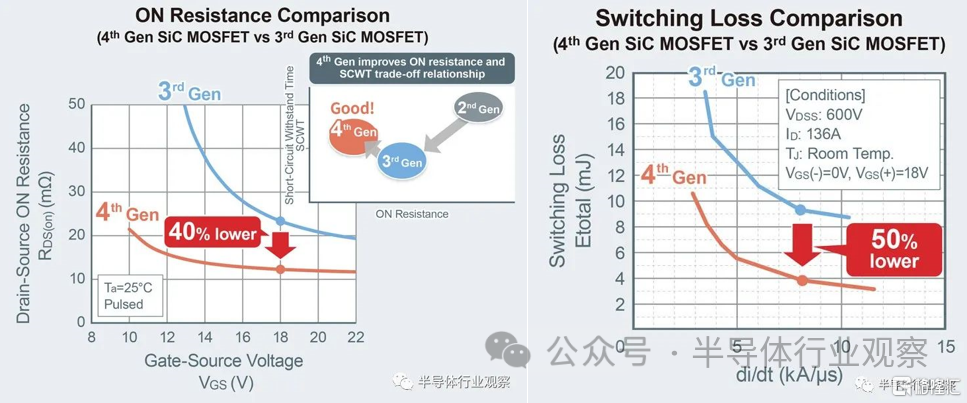

據了解,在第4代SiC MOSFET中,羅姆進一步改進了雙溝槽結構,成功在改善短路耐受時間的前提下,使導通電阻比第三代產品又降低約40%;同時通過大幅降低柵漏電容,成功地使开關損耗比以第三代產品降低約50%。

第4代SiC MOSFET與第3代的導通電阻、开關損耗比較(圖源:羅姆)

羅姆預測,第4代SiC MOSFET從2023年起在其銷售構成中的佔比逐漸增加,直至2024-2025年成爲銷售主力。

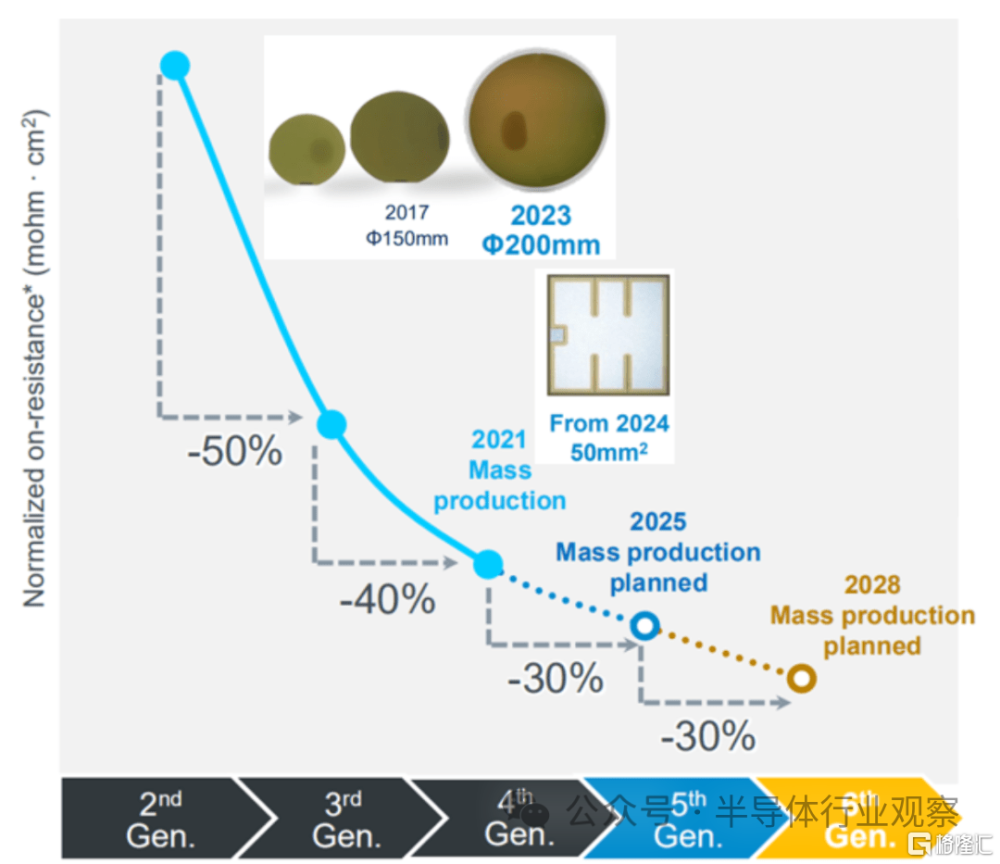

與其他尚在挑战首款量產溝槽柵產品的競爭對手相比,羅姆已領先數個身位。按照其產品路线圖,預計2025年和2028年將推出的第5代和第6代產品的導通電阻將會分別再降低30%。

羅姆的SiC MOSFET技術路线圖

英飛凌:半包溝槽結構

衆所周知,“挖坑”是英飛凌的祖傳手藝。

在硅基產品時代,英飛凌的溝槽型IGBT和溝槽型的MOSFET就獨步天下。隨着SiC時代的來臨,市面上大部分的SiC MOSFET都是平面型元胞,而英飛凌依然延續了溝槽結構的路线。

英飛凌半包溝槽SiC MOSFET結構示意圖

2017年,英飛凌報道了採用半邊導通結構的溝槽型SiC MOSFET器件,在柵極溝槽的一邊形成導電溝道。從上圖看到,參雜毗鄰溝槽中的區域是不對稱的,溝槽的左側壁包含了MOS溝道,它被對准到a-plane面,以實現最佳的溝道遷移率,溝槽底部的大部分被嵌入到溝槽底部下方的p型區域中。

該結構可保護溝槽拐角不受電場峰值影響,提高器件可靠性,同時能進一步提升器件耐壓,使得开關控制良好,動態損耗非常低。特別是,該特性對於抑制使用半橋的拓撲中寄生導通引起的額外損耗至關重要。

英飛凌的CoolSiC MOSFET溝槽分立器件系列,採用英飛凌獨特的溝槽的方式,爲其系統設計帶來了許多好處,包括高可靠性、效率提高、實現高开關頻率和高功率密度,降低系統復雜性和總系統成本。

英飛凌在2016年推出了第一代CoolSiC系列SiC MOSFET,並在2022年更新了第二代產品,相比第一代增強了25%-30%的載電流能力。

產能方面,英飛凌目前主要通過特有的“冷切割”技術,減少晶錠切割過程中材料的浪費,未來可以在相同晶錠中獲得多一倍的碳化硅襯底來增加產能。另一方面,英飛凌去年宣布投資超過20億歐元,對位於馬來西亞的晶圓廠進行擴建,專門針對碳化硅晶圓進行擴產。

意法半導體:深挖平面潛力,布局溝槽

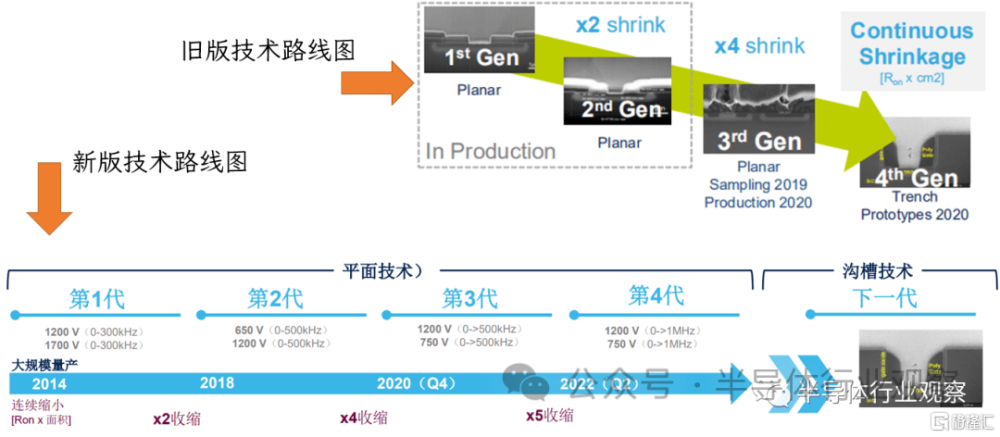

據Yole數據統計,全球碳化硅功率器件市場份額最高的廠商就是意法半導體(ST),同時憑借與特斯拉的合作,ST的SiC MOSFET產品也是最早在電動汽車上被大規模應用的,自Model3車型开始,特斯拉就一直大規模採用ST供應的碳化硅模塊。

在芯片設計上,意法半導體持續深挖平面設計碳化硅MOSFET的技術潛力,2022年推出了第4代平面柵SiC MOSFET。相比上一代產品,第4代平面柵碳化硅的性能有所進步,包括導通電阻減少15%,工作頻率增加一倍至1MHz。

而之前規劃的溝槽柵產品則順延成爲意法半導體的第5代SiC MOSFET,目前應該在研發階段,預計2025年量產。

意法半導體SiC MOSFET路线圖

(圖源:ST)

相比於平面型SiC MOSFET,溝槽型SiC MOSFET可以具有較小的導通電阻,寄生電容較小的同時开關性能更強。

產能方面,ST此前計劃在2022財年投入21億美元來擴大產能,包括擴建原有的6英寸碳化硅晶圓廠、2022投入運營的新加坡6英寸碳化硅晶圓廠。同時,2019年ST收購的瑞典碳化硅襯底生產商Norstel也开始進行8英寸碳化硅材料的測試,預計會在2025年前後可以在新加坡8英寸產线中應用。

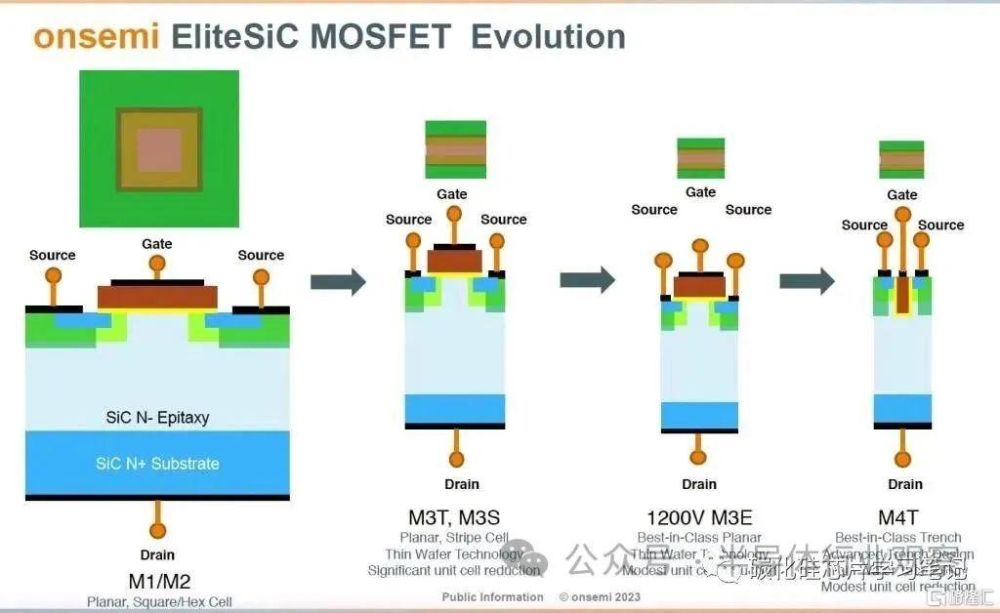

安森美半導體:溝槽型產品在即

2021年第3季度,隨着收購襯底供應商GTAT的通過,安森美搭建了從碳化硅晶錠、襯底、器件生產到模塊封裝的垂直整合模式。

雖然其中一些項目的技術實力與各領域領先企業還有所差距,但其整體實力卻更爲均衡:與襯底龍頭Wolfspeed相比,安森美的模塊封測和量產經驗略勝一籌;與器件設計實力超群的英飛凌相比,安森美又有來自GTAT碳化硅材料的加成。

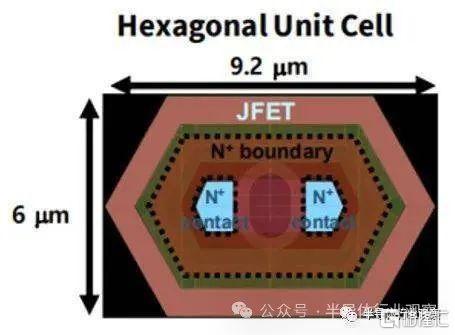

從產品結構來看,安森美的第1代碳化硅MOSFET技術(M1)採用平面設計,耐壓等級爲1200V。之後從中衍生出900V和750V耐壓的規格,微觀結構也改爲Hex Cell設計,這兩個改動相疊加使得碳化硅MOSFET的導通電阻降低了35%左右。目前安森美推出的大部分碳化硅產品均基於M1與其衍生出的M2平台。

目前最新的一代碳化硅技術(M3)仍然採用平面技術,但是改爲受專利保護的Strip Cell設計,導通性能較上一代衍生版本再提高了16%。這一代產品將逐漸成爲公司的主力車規碳化硅平台,在電壓規格上覆蓋電動汽車主流的400V和800V平台。

據了解,安森美的下一代技術平台M4則會從平面結構升級爲溝槽結構。與初代碳化硅技術相比,溝槽結構的SiC MOSFET在相同載電流的要求下可以減少相當的芯片面積。如果再加上M4平台可能採用8英寸晶圓生產,預期M4的成本較之前將顯著降低。

事實上,安森美在溝槽柵方面已經研究了很多年,也有很多樣品在進行內部測試,其認爲唯一的問題在於,過早的推出溝槽柵產品在可靠性方面還有一定的風險。所以安森美正在進行可靠性優化,提升溝槽柵的利用率。

同時,在提升可靠性方面,安森美也在對溝槽柵進行摸底,在標准測試的基礎上加一些認爲有風險的測試點,力圖將風險搞清楚。

另外,從封裝角度講,安森美提供各種不同的封裝選項,還將推出下一代設計很強的封裝,通過封裝的不斷迭代來適配不同的需求。

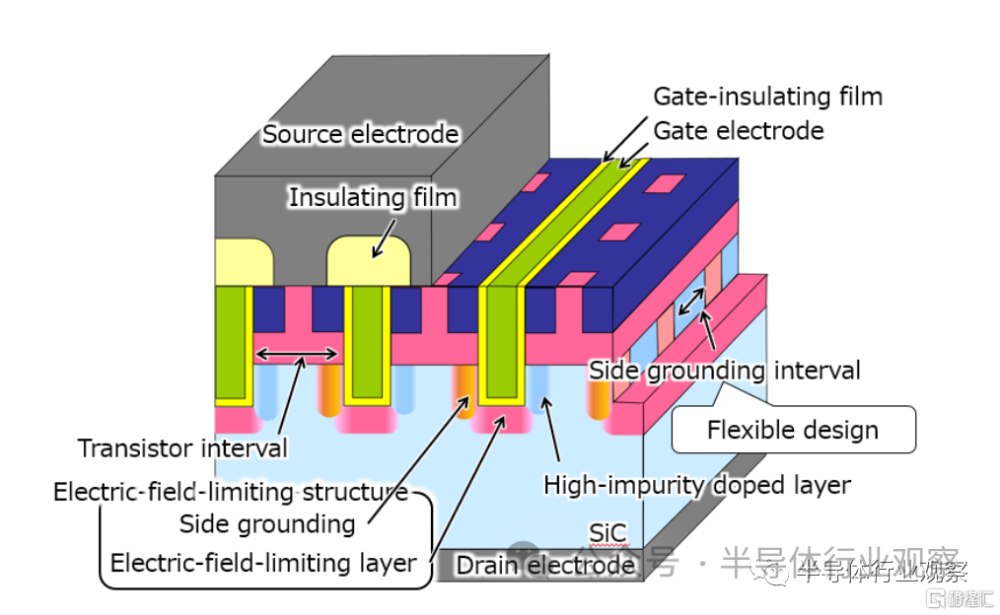

三菱電機:獨特電場限制結構

2019年,三菱電機也开發出了一種溝槽的SiC MOSFET,爲了解決溝槽型的柵極絕緣膜在高電壓下的斷裂問題,三菱電機基於在結構設計階段進行的先進模擬,开發了一種獨特的電場限制結構,將應用於柵絕緣薄膜的電場減小到常規平面型水平,使柵絕緣薄膜在高電壓下獲得更高的可靠性。

三菱電機的新型溝槽型SiC MOSFET結構示意圖

(圖源:三菱電機)

三菱電機利用獨特的電場限制結構確保器件可靠性,通過注入鋁和氮來改變半導體層的電氣特性,從而保護柵極絕緣膜。

具體來看,在垂直溝槽方向注入鋁元素,使溝槽底部形成電場限制層,再通過其新技術斜向注入鋁,形成連接電場場限制層和源極的側接地,並斜向注入氮元素,再局部形成更容易導電的高濃度摻雜層。電場限制層將施加在柵極絕緣膜上的電場降低到傳統平面結構水平,保證耐壓的同時,提高器件的可靠性。連接電場限制層和源極的側接地,實現了高速开關動作,減少开關損耗。

與平面結構相比,溝槽型器件Cell pitch更小,所以功率器件能排列更多的元胞。元胞高密度排列使得流動的電流變多,但各柵極的之間的間隔太小就會導致路徑變窄,電流流動困難。將氮元素斜向注入,在局部形成更容易導電的高濃度摻雜層,使電流路徑上的電流變得容易傳輸,從而降低電流通路的電阻。與沒用高濃度層相比,電阻率降低了約25%。

Wolfspeed:平面柵SiC MOSFET優勢未耗盡

作爲一家在SiC行業中浸潤了超過30年的企業,Wolfspeed及其前身Cree在1991年就推出了第一片量產碳化硅襯底。深厚的經驗積累和歷史沉澱讓Wolfspeed的碳化硅襯底性能和質量獨佔鰲頭,就連意法半導體、英飛凌和安森美等同行業競爭對手都不得不花費上億美元向其採購。因此,Wolfspeed的碳化硅產品獲得了至關重要的先發優勢,成爲了整個碳化硅行業的風向標。

在設計方面,Wolfspeed的碳化硅MOSFET採用平面設計,目前處於第3代,涵蓋650V到1200V之間的多個電壓規格。與之前兩代產品相比,Gen3 平面MOSFET採用六邊形晶胞微觀設計,導通電阻較上一代Strip Cell減少了16%。

Wolfspeed Gen3 SiC MOSFET採用Hex Cell的平面技術(來源:Wolfspeed)

據了解,Wolfspeed下一代產品將是溝槽柵設計,目前Gen4溝槽柵MOSFET仍在开發中,具體量產時間還沒有透露。

盡管也在布局溝槽結構,但從一开始就致力於碳化硅二極管和MOSFET开發的Wolfspeed認爲,平面柵SiC MOSFET的技術優勢遠未耗盡。

Wolfspeed聯合創始人John Palmour曾表示:“因爲溝槽MOSFET有更好的導通電阻,這是關鍵性能指標。只要我們在導通電阻方面遠遠領先溝槽SiC MOSFET,我認爲沒有理由改變這一點,何況我們還將繼續改進平面SiC MOSFET。客戶不應該關心它是平面MOSFET還是溝槽MOSFET,重要的是特定導通電阻。事實上,我們也不在乎哪種技術路线,我們只關注哪種設計能給客戶帶來最大的利益。”

簡而言之,平面結構還有深挖的空間,做好可靠性,也一樣有市場。

富士電機:全SiC溝槽MOSFET

早在2016年,富士電機就开發了用於全SiC模塊的1200V SiC溝槽MOSFET,實現了3.5mΩcm2的低比電阻,閾值電壓爲5V,同時保持用於打开和關閉電流的“通道”的高可靠性。

由此,與以前的平面結構相比,成功地將電阻率降低了50%以上。此外,富士電機還开發了一種採用獨特引腳連接結構的高電流密度專用SiC模塊,充分發揮了SiC器件的優點。富士電機已經使用該設備實現了All-SiC模塊。

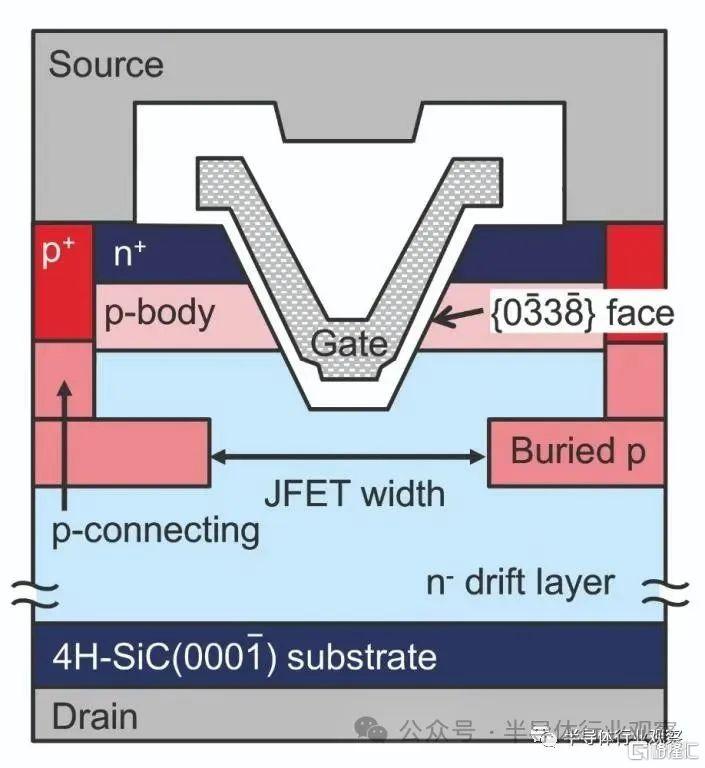

日本住友:V形溝槽

2016年,住友公司研制出具有厚底部氧化層的V型溝槽SiC MOSFET器件樣品,進一步提高了器件的柵氧可靠性和閾值穩定性。

住友電工的SiC VMOSFET橫截面圖

(圖源:住友電工)

住友電工利用獨特的晶面新开發了V形槽溝槽MOSFET。V-MOSFET具有高效率、高阻斷電壓、惡劣環境下的高穩定性等優越特性,實現了大電流(單芯片200A),適用於EV和HEV。此外,住友電工正在與國家先進工業科學技術研究所合作开發具有世界最低導通電阻的下一代 V-MOSFET。

日本電裝:U形溝槽

2023年3月,電裝(DENSO)宣布已开發出首款採用SiC半導體的逆變器。

其中,電裝獨特的溝槽型MOS結構採用其專利電場緩和技術的溝槽柵極半導體器件,提高了每個芯片的輸出,因爲它們減少了由發熱引起的功率損耗,獨特的結構實現了高電壓和低導通電阻操作。

電裝的溝槽柵結構(圖源:電裝)

有資料顯示,電裝類似於住友的溝槽結構,只是改爲了U形溝槽。

圖源:松哥電源

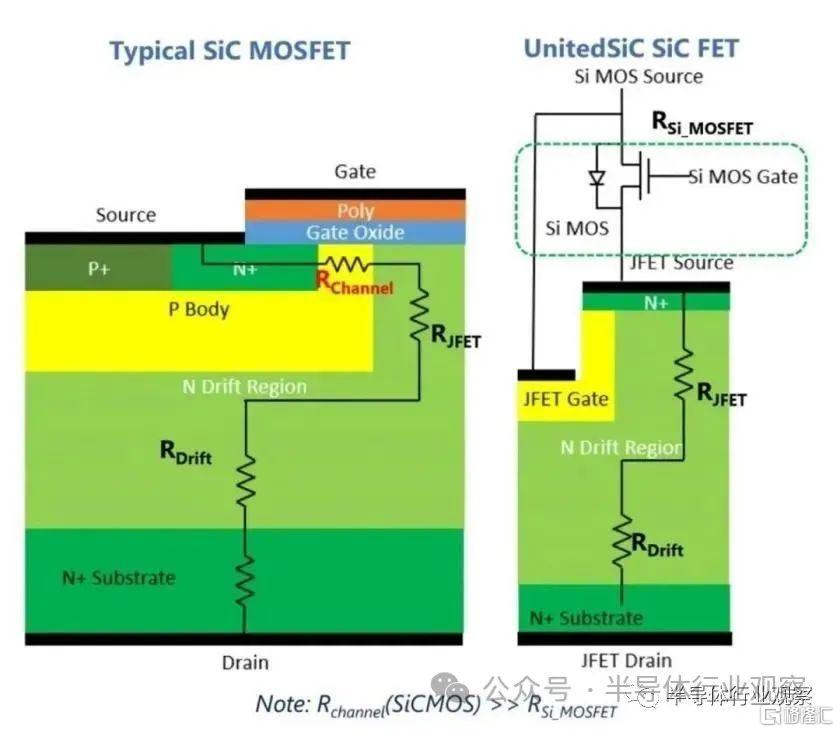

Qorvo:高密度溝槽SiC JFET結構

Qorvo的SiC技術主要來源於2021年收購的UnitedSiC,如今SiC也是Qorvo未來發展的重中之重。

據了解,不同於傳統的SiC MOSFET設計,Qorvo另闢新徑,其SiC MOSFET採用了高密度溝槽 SiC JFET結構,SiC MOSFET中的溝道電阻Rchannel被SiC FET中低壓硅MOSFET的電阻所取代,後者的反轉層電子遷移率要好得多,實現了超低單位面積導通電阻,因此損耗也更低。該結構與低電壓 Si MOSFET 共同封裝,SiC FET的晶粒面積也相對較小。

SiC MOSFET(左)和 Qorvo的SiC FET(右)架構對比(圖源:Qorvo)

Qorvo擴充了其1200V產品系列,將其突破性的第四代SiC FET技術推廣到電壓更高的應用中,產品規格從23mΩ-70mΩ,瞄准800V電動汽車車載充電器(OBC)和直流轉換器等應用市場。

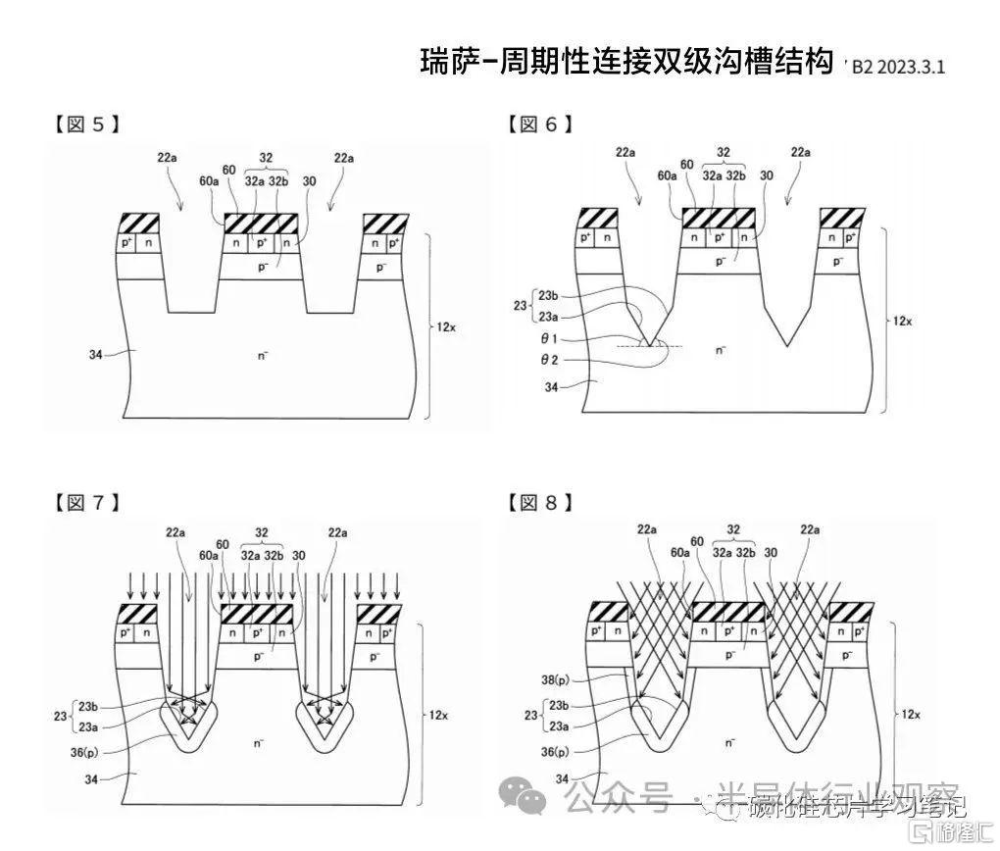

瑞薩電子:變異雙級溝槽MOSFET

據了解,瑞薩電子在2023年剛申請了專利,准備研究碳化硅溝槽結構,簡稱"周期性連接,變異雙級溝槽MOSFET”。

圖源:碳化硅芯片學習筆記

寫在最後

總而言之,提高SiC MOSFET性能的幾個重要指標,包括更小的元胞間距、更低的比導通阻、更低的开關損耗、更好的柵氧保護,幾乎都指向了溝槽柵結構。

從行業整體來看,目前量產溝槽型SiC MOSFET的主要是歐美日等國際SiC廠商。從國際廠商的布局來看,溝槽柵SiC MOSFET會是未來更具競爭力的方案。

從2015年第一款量產溝槽柵SiC MOSFET產品推出到現在過去了近9年時間,衆多企業都在开發溝槽柵產品,但目前市面上能夠推出量產產品的廠商並不算多。

當然,設計、制造高性能的溝槽柵SiC MOSFET也是國內SiC功率器件發展的當務之急,部分企業已將研究的重心轉移至溝槽柵SiC MOSFET。但需要注意的是,國際SiC巨頭在SiC MOSFET領域布局多年,積累了不少專利。溝槽結構的高專利壁壘也是國產廠商要邁過去的坎兒。

根據“碳化硅芯片學習筆記”作者的說法:“溝槽SiC MOSFET成套工藝及結構IP,是未來十年碳化硅競爭的入場券!”在目前整體SiC市場持續高速增長的時期,提前布局合適的技術路线,才有機會在未來新的應用市場上佔得先機。

標題:SiC,全民“挖坑”

地址:https://www.iknowplus.com/post/70320.html