新技術浪潮與變革下,國產EDA如何破局?

衆所周知,芯片是現代科技的核心關鍵和技術底座。

而EDA作爲集成電路產業鏈上遊的關鍵環節,是設計大規模集成電路必備的工具,堪稱“芯片之母”,也是一個公認市場規模本身不大,但卻能撬動半導體產業鏈的關鍵“槓杆”。

近年來,隨着全球芯片市場的動蕩和變革,強韌、高效和創新的EDA生態建設成爲了業界迫切的需求。

在此背景和趨勢下,在11月10日舉行的ICCAD 2023高峰論壇上,上海思爾芯技術股份有限公司(下文簡稱“思爾芯”)副總裁陳英仁帶來了《共贏 EDA新生態:全方位解決方案與多元合作》的主題演講,圍繞數字EDA的產業破局、技術創新,以及如何鑄造國產EDA新生態等話題進行了精彩分享,同時也重點展示了思爾芯在數字EDA領域的全面解決方案。

思爾芯副總裁陳英仁

陳英仁表示,盡管面對國際巨頭的市場競爭和圍追堵截,面對技術積累、人才儲備、生態缺失的諸多短板,但本土EDA廠商近年來在政策和資本的大力扶持、產業鏈夥伴協同合作,以及行業人才不斷取得突破的趨勢下,如雨後春筍般爆發,迎難而上。

他強調,“在EDA新生態中,除了追求經濟回報外,更要注重與合作夥伴建立基於‘利+義’”的深度合作關系,共同推動行業的繁榮與進步。”

所謂利,即對利益的追求,EDA技術的革新一方面可以給資本帶來利益回報,另一方面可以幫助客戶提高設計效率,降低成本,增強競爭力,爲客戶帶來經濟效益;義,則是對雙贏的新定義,EDA企業與合作夥伴不僅僅是經濟利益,更重要的是合作與責任的共同承擔。

不難理解,EDA與國產技術同行,秉承“利+義”的原則,打造有溫度的合作關系,才是共築EDA產業新生態的基礎。

新技術浪潮推動EDA創新與變革

當前,除了本土EDA廠商和行業夥伴自身努力謀發展之外,芯片領域新興技術層出不窮,新興架構、標准、需求和理念也在不斷推動行業進步。當下RISC-V、Chiplet和AI技術成爲行業高頻詞,其發展和成熟給EDA廠商帶來了新挑战和新機遇。

陳英仁表示,面對RISC-V、AI、Chiplet等技術的快速發展,EDA技術必須進行創新和變革,以滿足新的設計和實現需求。

RISC-V爲設計帶來更多可能性

首先來看RISC-V,RISC-V架構從設計理念上摒棄了“歷史包袱”,具有精簡、低功耗、模塊化、可擴展、开放开源等技術優勢,旨在爲芯片設計帶來更多可能性。

尤其是在物聯網(IoT)領域,开源架構RISC-V的出現,進一步點燃了新晉者的熱情。

在逐漸走向成熟的IoT行業中,RISC-V以其極具多樣性、低功耗、高安全性和成本效益的優勢,展現出巨大的潛力。更重要的是,其开源和高度可定制的特性賦予了芯片設計企業更大的自主權,從而滿足了多樣化的客戶需求。

根據RISC-V基金會數據,2022年採用RISC-V架構的處理器核已出貨100億顆,其中絕大多數出貨都集中在MCU和IoT領域。預計到2025年,RISC-V架構的處理器核出貨量將突破800億顆。在出貨量暴增的同時,RISC-V應用場景不再局限於低功耗物聯網領域,而是逐漸向手機、電腦、汽車、數據中心等應用領域拓展。

不僅如此,RISC-V作爲一種开放指令集架構,也爲中國芯片產業提供了一個新的選擇和機會。隨着國際貿易衝突和“逆全球化”加劇,國內开始加速擁抱开源RISC-V架構發展,以避免在主流CPU芯片架構上受制於人,實現更多的自主創新和供應鏈安全。

去年出貨量超100億顆的RISC-V架構芯片,國內出貨量已經佔據一半,不僅有衆多國內企業和科研機構加入了RISC-V國際基金會,還成立了中國开放指令生態聯盟和國內首個RISC-V專利聯盟,致力於推動中國RISC-V芯片生態建設。

RISC-V技術正憑借其开放性、高效性和卓越的可擴展性,重新定義計算的未來。不過,任何技術的發展都存在兩面性,RISC-V在提供自主供應鏈機會,加速技術迭代的同時,其开放協作模式也帶來了諸多挑战。

RISC-V的劣勢在於其還處於發展初期,還沒有形成一個完善而統一的技術體系和商業模式。陳英仁指出,在標准細節定義、碎片化&穩定性以及EDA支持方面,RISC-V還存在不足,爲芯片設計帶來挑战。

隨着RISC-V技術深入各領域,它以开源、簡潔和高度可擴展的特性正逐步塑造未來。盡管RISC-V潛力巨大,其生態系統仍存在待完善之處。特別是其獨立、靈活和彈性的設計理念讓系統碎片化的問題劇增。

EDA的任務就是傾聽客戶需求,來滿足他們在不同應用對產品設計或生態系統的支持。

爲了應對這些挑战,思爾芯爲RISC-V提供了涵蓋微架構分析、系統整合、規範符合性測試以及軟件性能評估的一系列優化解決方案。通過思爾芯的“芯神匠”的系統&應用性能分析、“芯神瞳”的評估架構配置/軟件性能分析、“芯神鼎”的規範符合性測試等策略,構建一個更高效和穩定的RISC-V平台。

據悉,思爾芯還在助力北京开源芯片研究院“香山”項目的不斷演進。

“香山”高性能RISC-V處理器是一個由中國科學院計算技術研究所孕育出的开源項目,從“香山”的第一代到目前的第三代,其背後的技術支撐與演進都離不开思爾芯的助力,开芯院都採用了思爾芯的“芯神瞳”原型驗證解決方案,加速其技術的演進與應用落地。

在集成電路和微處理器設計中,原型驗證是不可或缺的一環,它涉及到在真實硬件上驗證設計的功能、性能和可靠性。思爾芯爲“香山”提供了一個針對性的解決方案——芯神瞳VU19P原型驗證系統,使“香山”能夠高效地完成SPEC跑分驗證、IO驗證以及BSP驅動的开發等工作,涵蓋了從硬件設計到軟件集成的整個生命周期的不同方面。

Chiplet技術:未來算力芯片的解決方案

RISC-V之外,當下Chiplet技術的發展也給本土EDA廠商帶來“換道超車”的新機遇。

Chiplet又稱“小芯片”或“芯粒”,通過將不同工藝節點和不同材質的芯片通過先進封裝技術集成在一起,形成一個系統芯片,實現了一種新形式的IP復用。

在芯片產業,由於Chiplet能夠緩解性能、功耗和成本的限制,大幅度降低對最先進工藝的要求和成本負擔,這一技術方向受到行業追捧,AMD、英特爾等公司已採用Chiplet方案設計芯片,此方案也被稱爲“異構集成”。

與RISC-V技術類似,Chiplet新趨勢背後也面臨新挑战。

陳英仁表示,Chiplet趨勢下,更多異構芯片和各類總线的加入,整個過程將會變得更加復雜,對EDA工具也提出了新要求。一方面,芯片的設計必須適應不同IP、不同Chiplet組合的復雜產品形態,異構集成系統中接口與標准的統一性,設計者需在異構芯片的性能與靈活性之間找到平衡;另一方面,Chiplet正重塑半導體產業鏈, 推動新的EDA工具鏈,以及IP、設計、後端封裝/生產等新的上下遊生態結合,催生新的商業模式。

針對此類需求,EDA業內提出了混合異構驗證方法,成熟的Chiplet,RTL-Ready IP,System Modeling IP可以在一個系統中同時建模驗證,並發揮Chiplet、RTL-Ready IP的高速優勢,也支持System Modeling IP的靈活配置功能。

據悉,對於異構芯片設計驗證的需求,思爾芯也提出了基於驗證雲系統的統一驗證平台,平台融合架構設計、原型驗證等不同解決方案,以期實現高效快速驗證。

AI + EDA:適應存儲和算力爆炸性增長的挑战

此外,在ChatGPT引領的新一代生成式AI浪潮下,隨着AI應用的持續增長,爲芯片和EDA生態帶來新機遇的同時,也引發了對算力基礎設施的需求飆升,而作爲算力基礎的高性能芯片,存儲與算力的爆發式增長對SoC設計和驗證施加了巨大壓力。

陳英仁表示,AI技術的發展不僅加速了更復雜的計算需求、更強的功能性和更快的數據傳輸速度,同時也爲芯片研發人員帶來了前所未有的挑战,傳統的芯片設計方法已經不能適應當前的市場需求;此外,AI引擎一改傳統的馮諾·依曼架構,在新的框架需求下,探索應用驅動算法、算法驅動軟件,以及軟硬件架構靈活協同設計,引領芯片設計的下一場革新,芯片設計行業迫切需要EDA的創新來應對AI時代的新變革。

尤爲值得關注的是,在集成電路規模越發龐大的現實情況下,從設計到流片的全流程中,驗證變得尤爲重要。因爲有效的驗證不僅能確保電路設計層面的完善,還保證了其在實際應用中的穩定運行,從而降低修正和調整的成本和時間。

爲了應對這一挑战並縮短驗證周期,硬件仿真成爲了超大規模集成電路驗證的關鍵工具。同時,AI算力的飛速增長不僅促進了EDA工具的快速演進,還與EDA工具結合,催生了一種“雙向加速”的良性循環。

對此,思爾芯推出了首款國產企業級硬件仿真系統——芯神鼎OmniArk,該硬件仿真系統採用了由AI驅動的智能編譯引擎,能夠在編譯流程中極大地減少編譯時間和內存佔用,實現增量編譯,並能智能匹配P&R策略,從而顯著提高布线的成功率。

芯神鼎將AI應用於編譯流程,推動了芯片設計領域的發展,开啓了EDA驗證新時代。

此外,思爾芯的芯神瞳邏輯系統和邏輯模塊產品也是目前市場上頗具競爭力的原型驗證解決方案,其高性價比獲得了市場的青睞。前不久,思爾芯發布了最新一代原型驗證解決方案——芯神瞳邏輯系統S8-40,也爲當前如AI、GPU芯片等大存儲和大數據設計提供了有效的解決方案。

思爾芯,20年持續打造數字EDA全流程

整體來看,面對RISC-V、Chiplet、AI等技術的快速進展,EDA技術必須進行創新和變革,以滿足新的設計和實現需求。

在新技術引領的行業契機和挑战下,思爾芯致力於通過新技術的布局、前瞻性的探索,圍繞應用創新、軟硬交互和系統工程等多方面打造創新的生意模式,爲客戶創造更大價值。

陳英仁介紹道,面臨上述新技術對方便性與精准性的需求,思爾芯的工具作爲載體和平台,可以對新技術做虛和實的架構探索,結合不同EDA廠商、IP廠商、後端制造等產業鏈夥伴,一起爲客戶提供更有效的方案。

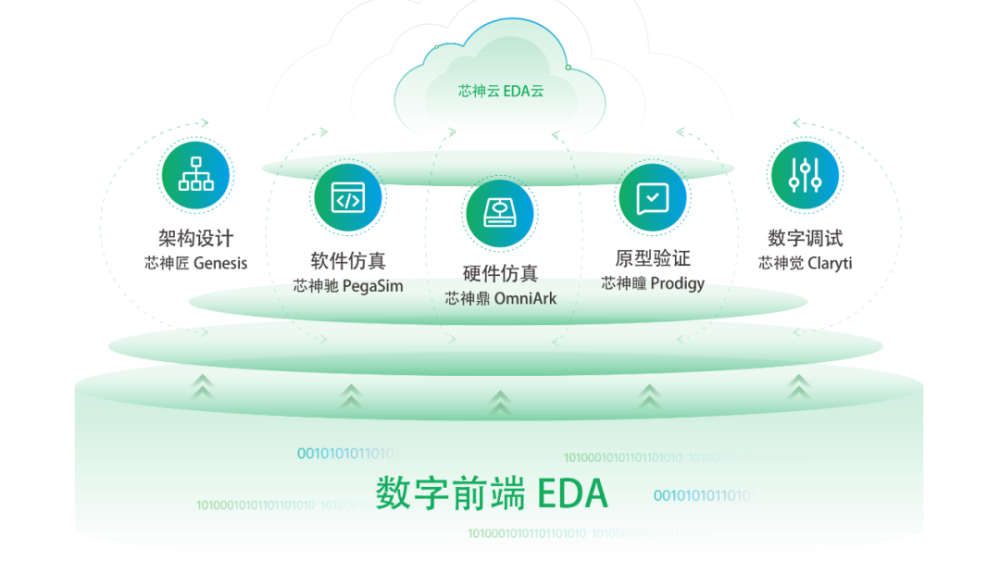

據了解,思爾芯於2004年在上海成立。近20年來,思爾芯持續發揮EDA技術優勢,致力於爲衆多的IC設計企業提供全方位、全流程和全覆蓋的產品組合。陳英仁表示,思爾芯專注於芯片數字前端領域,推出了一系列優質的數字EDA工具,如架構設計工具“芯神匠”、軟件仿真工具“芯神馳”、硬件仿真工具“芯神鼎”、原型驗證工具“芯神瞳”,以及提供全面的EDA雲服務,確保芯片設計流程能夠完整、准確地實現對需求規格的響應,從而加快芯片產品的开發進程。

當前,EDA逐步上雲已成趨勢。思爾芯是國內首家通過自主研發推出原型驗證雲服務的EDA企業。

在ICCAD論壇上,中國半導體行業協會集成電路設計分會理事長魏少軍教授表示,2023年中國大陸有3451家芯片設計企業,比去年增加了208家。但這3451家芯片設計企業廣泛分布在消費電子、工業、汽車、數據中心等多個行業。這些企業大多爲中小微企業,且大多面臨人手短缺,設計能力匱乏等問題,尤其是設計團隊在進行仿真和驗證時,往往缺乏大規模的算力集群支持。

對於AI和HPC這類對芯片設計要求更高的應用來說,不僅對开發團隊的創新提出了要求,也對其硬件計算資源提出了更高的要求,所以軟件上雲被提了出來。可以持續擴張的算力資源,爲設計與驗證提供了便利,大大降低了芯片設計自動化的效率,也降低了基礎設施的添置和管理成本。

在這一趨勢下,EDA廠商們紛紛开啓了自己的上雲之路,發展雲端EDA業務。

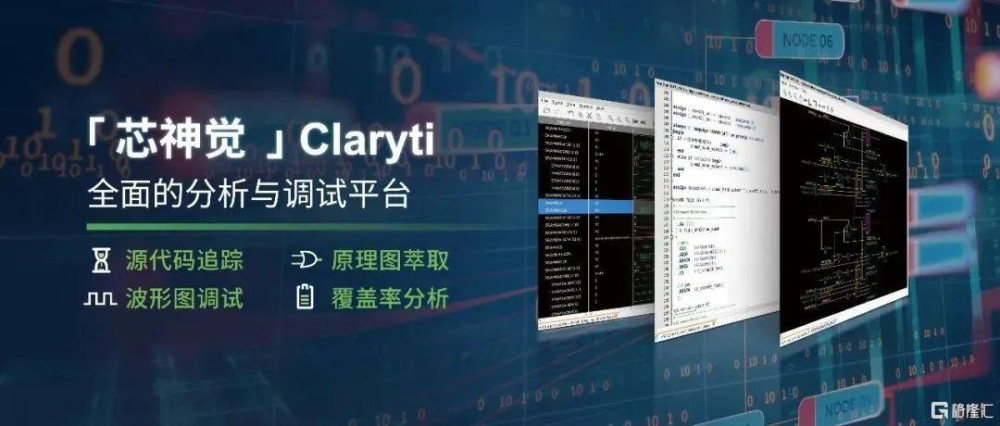

思爾芯重磅發布自研數字電路調試軟件“芯神覺”

與此同時,在ICCAD 2023上,思爾芯正式發布一款自主研發的數字電路調試軟件——“芯神覺”,這款全新的工具集成了源代碼追蹤、波形圖調試、原理圖萃取和覆蓋率分析等核心功能,旨在爲工程師提供一個全面、高效的分析與調試平台。利用先進的調試技術幫助开發者簡化整個調試過程,加速芯片开發。

“芯神覺”在與思爾芯的其他產品如軟件仿真、硬件仿真以及原型驗證等工具靈活銜接,實現深度融合後,可以爲芯片工程師打造一個既統一又高效的設計環境。這不僅極大地簡化了繁復的調試工作,而且使得整個調試流程變得更加流暢和高效,顯著提升了復雜芯片設計驗證的效率。

思爾芯在EDA領域的技術實力受到了業界的廣泛認可,通過多年耕耘,已在數字前端EDA領域構築了技術與市場的雙優勢地位,已與超過600家國內外企業建立了良好的合作關系。並參與了我國 EDA 團體標准的制定,承擔了多項國家及地方重大科研項目,獲國家級專精特新“小巨人”企業、國家工業軟件優秀產品、上海市級企業技術中心等多項榮譽資質。

隨着本次“芯神覺”新品的推出,將進一步增強思爾芯數字前端EDA解決方案,爲芯片設計企業提供了一個更全面的產品和服務組合。

寫在最後

作爲芯片設計領域的“基座技術”,在RISC-V、Chiplet、AI等新技術趨勢推動下,EDA的全流程創新將撬動芯片產業的巨大變革。

同時,中國作爲全球規模最大、增速最快的集成電路市場,在復雜的國際貿易關系和“國產替代”的時代浪潮下,國產EDA迎來巨大的發展空間和市場潛力。

諸多機會促進發展,國內EDA未來可期。

在這個過程中,以思爾芯爲代表的國產EDA企業,正着力EDA產業的破局之路,力圖鑄造國產EDA新生態。

標題:新技術浪潮與變革下,國產EDA如何破局?

地址:https://www.iknowplus.com/post/52316.html