2nm,大战打響!

雖然3nm方興未艾,但圍繞着2nm工藝的爭奪战已經正式打響。

在今年2月份,據韓媒Sedaily 報道,稱Samsung 正在積極推進2nm 工藝,並且已討論爲高通和Samsung 的LSI 部門生產原型產品,當前有一款未命名的Exynos 可能正處於早期測試階段;三月份的時候,Marvell宣布擴大與台積電的合作,以开發業界首個生產針對加速基礎設施優化的 2nm 半導體的技術平台。

本月,蘋果首席運營官傑夫·威廉姆斯 (Jeff Williams) 被曝低調到訪台積電,其此行的目的主要是爲了確保公司2nm的產能供給。

有見及此,三大晶圓代工廠台積電、三星和Intel正在圍繞2nm明爭暗鬥,日本新興晶圓廠Rapidus也正在摩拳擦掌,躍躍欲試。

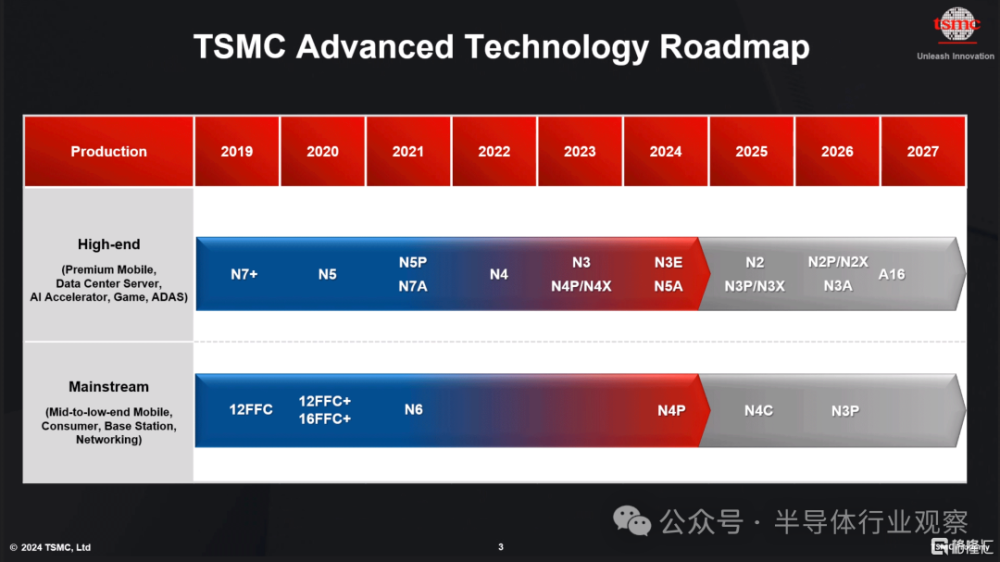

台積電,如期量產

圍繞着台積電的2nm,最近有很多傳言。

但據台媒工商時報報道,台積電工藝开發副總經理張曉剛在5月23日的論壇上表示,“2納米工藝开發進展順利”,“按計劃2025年左右可實現量產”,以此駁斥了“台積電因技術問題將2納米工藝全面量產推遲至2026年”的猜測。

台積電在官方網站中介紹2nm的時候說到,隨着不斷突破先進邏輯技術的擴展界限,台積電已經遠遠超越了 FinFET,實現了 2 納米節點的商業化,這是以納米片晶體管爲特色的一流邏輯技術。台積電業界領先的 N2 技術具有出色的低 Vdd 性能,非常適合移動和可穿戴應用。此外,N2 的超薄堆疊納米片爲 HPC 帶來了全新級別的節能計算。還將添加背面電源軌以進一步提高性能。

台積電認爲,對於希望利用納米片技術無與倫比的優勢來釋放前所未有的創新能力的客戶來說,台積電 N2 技術是一個战略選擇。

在四月份的北美峰會上,台積電也披露了2nm的更詳細的計劃。

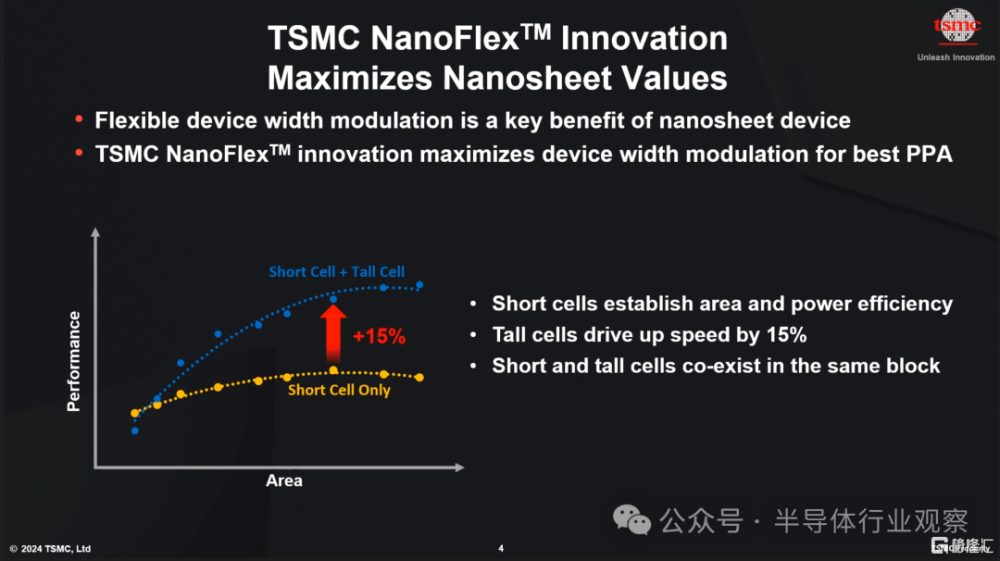

按照台積電當時所說,公司有望在 2025 年下半年开始在其第一代 GAAFET N2 節點上批量生產芯片,而 N2P 將在 2026 年底接替 N2——盡管沒有之前宣布的背面供電功能。同時,整個 N2 系列將增加台積電的全新 NanoFlex 功能,該功能允許芯片設計人員混合和匹配來自不同庫的單元,以優化性能、功率和面積 (PPA)。

相關報道表示,在本次峰會上,台積電的一項重要公告是台積電的 NanoFlex 技術,該技術將成爲該公司完整的 N2 系列生產節點(2 納米級、N2、N2P、N2X)的一部分。NanoFlex 將使芯片設計人員能夠在同一塊設計中混合和匹配來自不同庫(高性能、低功耗、面積高效)的單元,從而使設計人員能夠微調其芯片設計以提高性能或降低功耗。

台積電當代的 N3 制造工藝已經支持類似的功能 FinFlex,該功能還允許設計人員使用來自不同庫的單元。但由於 N2 依賴於全柵 (GAAFET) 納米片晶體管,因此 NanoFlex 爲台積電提供了一些額外的控制:首先,台積電可以優化溝道寬度以提高性能和功率,然後構建短單元(以提高面積和功率效率)或高單元(以提高 15% 的性能)。

台積電的強調,公司的N2 將於 2025 年進入風險生產,並於 2025 年下半年進入大批量生產 (HVM),因此看起來我們將在 2026 年看到 N2 芯片出現在零售設備中。與 N3E 相比,台積電預計 N2 將在相同功率下將性能提高 10% 至 15%,或在相同頻率和復雜度下將功耗降低 25% 至 30%。至於芯片密度,該代工廠正在考慮將密度提高 15%,以當代標准來看,這是一個很好的擴展程度。

繼 2nm之後,性能增強型 N2P 和電壓增強型 N2X 將於 2026 年問世。盡管台積電曾表示 N2P 將在 2026 年增加背面供電網絡 (BSPDN),但看起來情況並非如此,N2P 將使用常規供電電路。原因尚不清楚,但看起來該公司決定不爲 N2P 添加昂貴的功能,而是將其保留到下一代節點,該節點也將於 2026 年底向客戶提供。

不過,2nm仍有望在電源方面實現一項重大創新:超高性能金屬-絕緣體-金屬 (SHPMIM) 電容器,這些電容器的加入是爲了提高電源穩定性。SHPMIM 電容器的容量密度是台積電現有超高密度金屬-絕緣體-金屬 (SHDMIM) 電容器的兩倍多。此外,與上一代產品相比,新的 SHPMIM 電容器的薄層電阻 (Rs,單位爲歐姆/平方) 和通孔電阻 (Rc) 降低了 50%。

爲了生產2nm,台積電更是規劃了幾個工廠。

根據今年年年初的報道,台積電正准備在台灣建設兩座能夠生產 N2 芯片的制造廠。第一座工廠計劃位於新竹縣寶山附近,毗鄰其專門爲开發 N2 技術及其後續技術而建的 R1 研發中心。該工廠預計將於 2025 年下半年开始大批量生產 (HVM) 2nm 芯片。第二座能夠生產 N2 芯片的制造廠將位於高雄科學園區,該園區是高雄附近南台灣科學園區的一部分。該工廠的 HVM 啓動時間預計稍晚一些,可能在 2026 年左右。

此外,台積電正在努力獲得政府批准,在台中科學園區建造另一座具有 N2 能力的工廠。如果該公司在 2025 年开始建造該設施,該工廠最早可在 2027 年投入使用。

當然,拿到了美國政府補貼的台積電也會在那邊生產2nm。按照原規劃,台積電在美的第二座晶圓廠除了之前宣布的 3nm 技術外,還將採用下一代納米片晶體管生產世界上最先進的 2nm 工藝技術,並將於 2028 年开始生產。第三座晶圓廠將採用 2nm 或更先進的工藝生產芯片,並將於 2020 年底开始生產。

三星,積極應對

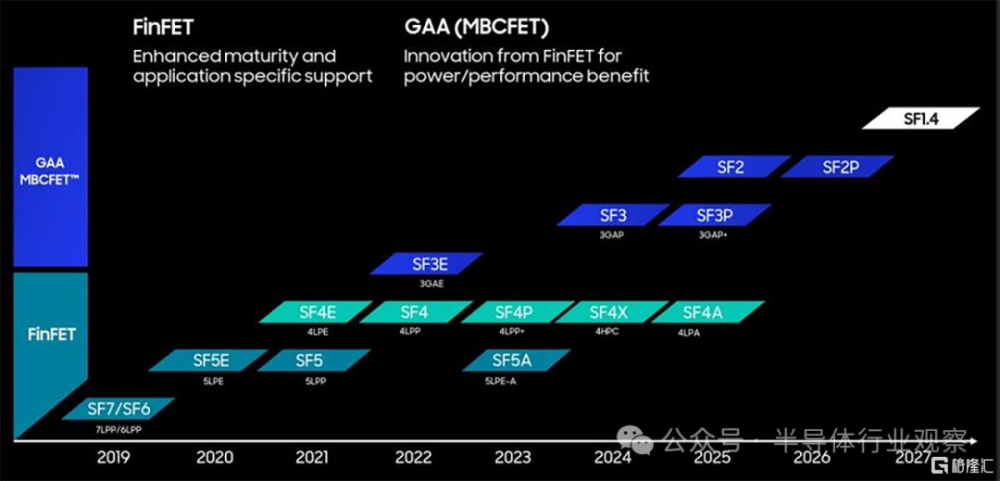

作爲首先量產3nm的晶圓廠,三星在2nm方面也積極應對。首先,是一條來自台媒Digitimes的傳言。

據報道,三星電子將其第二代 3nm 工藝更名爲“2nm 工藝”,預計將於 2024 年下半年开始量產。

盡管早在 2023 年底就有傳聞稱三星打算將第二代 3nm 工藝更名爲 2nm,但ZDNet Korea援引業內人士的話報道稱,三星已开始通知客戶和合作夥伴,將在 2024 年初將“第二代 3nm 工藝”更名爲“2nm 工藝”。

業內人士透露,他們已經收到三星關於更名的通知,並因此需要重新籤訂合同。

分析認爲,更名可能有助於三星營銷其代工服務。這也不是三星第一次更名其制造工藝。2020 年,在從 7nm 過渡到 5nm 工藝時,三星將“第二代 7nm 工藝”更名爲“5nm 工藝”。

三星於 2022 年 6 月在全球率先量產採用全柵極 (GAA) 工藝的 3nm 芯片。該公司計劃於 2024 年开始量產其第二代 3nm 工藝,並於 2025 年开始量產 2nm 工藝。更名後,三星可能會整合第二代 3nm 和 2nm 工藝。據推測,三星最早可能在 2024 年下半年开始量產 2nm 芯片。

美媒Tomshardware則在報道中指出,三星代工廠將於 6 月舉辦的 VLSI 研討會上詳細介紹其採用全柵 (GAA) 晶體管的第三代工藝技術。該技術稱爲 SF2,將成爲該公司最初的 2nm 級制造工藝。該節點預計將在性能和效率方面提供顯着改進。

根據該公司自己的描述,即將到來的節點將通過獨特的外延和集成工藝進一步完善三星的多橋通道場效應晶體管架構。這將使其能夠將晶體管性能提高 11-46%,與未指定的基於 FinFET 的工藝技術相比,可變性降低 26%,同時將泄漏降低約 50%。

三星在描述中寫道:“通過引入獨特的外延和集成工藝,第三代 MBCFET(SF2)能夠充分發揮產品性能,從而最大程度地提高柵極環繞優勢,克服了產品增益與縮放和 GAA 結構衝突的問題。”三星表示,SF2 可將窄晶體管(N 型)的性能提高 29%,將 P 型的性能提高 46%,將寬晶體管的性能分別提高 11% 和 23%。此外,與 FinFET 技術相比,它可將晶體管整體變化降低 26%,並將產品漏電降低約 50%。該工藝還通過與客戶加強設計技術共同優化 (DTCO) 合作,爲未來的技術進步奠定了基礎。

韓媒Business Korea更是報道稱,三星不僅在突破技術界限,而且還在加強其 2nm 級制造工藝的生態系統。該公司正在與 50 多個知識產權 (IP) 合作夥伴合作,擁有 4,000 多個 IP 。但出於顯而易見的原因,其中只有少數是針對 GAA 節點,尤其是 SF2。與此同時,今年早些時候,三星和 Arm 籤署了一項協議,共同優化 Cortex-X 和 Cortex-A 內核,以適應三星的全柵極晶體管制造技術。

據稱,三星表示,SF2 的設計基礎設施(PDK、EDA 工具和授權 IP)將於 2024 年第二季度完成。一旦完成,三星的芯片开發合作夥伴將能夠开始爲該生產節點設計產品。

與此相關,三星有望於今年开始使用其第二代 3nm 級制造工藝(稱爲 SF3)制造芯片。三星的第一代 3nm 級節點 SF3E 並不是特別成功,因爲該公司主要使用這項技術生產加密貨幣挖礦芯片。但三星希望其 SF3 節點能夠得到更廣泛的應用,包括更復雜的設計,包括數據中心產品。

據報道,三星將於2025 年开始大規模生產用於移動應用的 2 納米工藝,並在2026年推進2納米技術應用於超級計算機和計算機市場的高性能計算(HPC)芯片,到2027年,2nm工藝將應用於汽車芯片。

值得一提的是,SF2 可能是第一個引入背面供電的三星代工廠節點。據悉,三星代工廠已在兩款 ARM 芯片上測試了 BSPDN 技術,結果芯片尺寸分別縮小了 10% 和 19%,性能和效率最高提升了 9%。該報道還稱,測試結果超出了公司的性能目標。

關於三星的2nm晶圓廠,筆者並沒有找到太多信息。但有報道表示,該公司計劃到 2047 年在韓國首爾附近的一個“大型集群”半導體項目中總投資 500 萬億韓元(3710 億美元),該公司希望在這裏生產 2nm 芯片。據介紹,該集群包括 13 家芯片工廠和 3 個研究設施,將橫跨京畿道的幾個城市。

和台積電一樣,拿到了美國補貼的三星,也將在大洋彼岸生產2nm芯片。報道披露,三星將在德克薩斯州泰勒市建造一座新工廠,該工廠將從 2026 年开始生產尖端的 2nm 芯片。

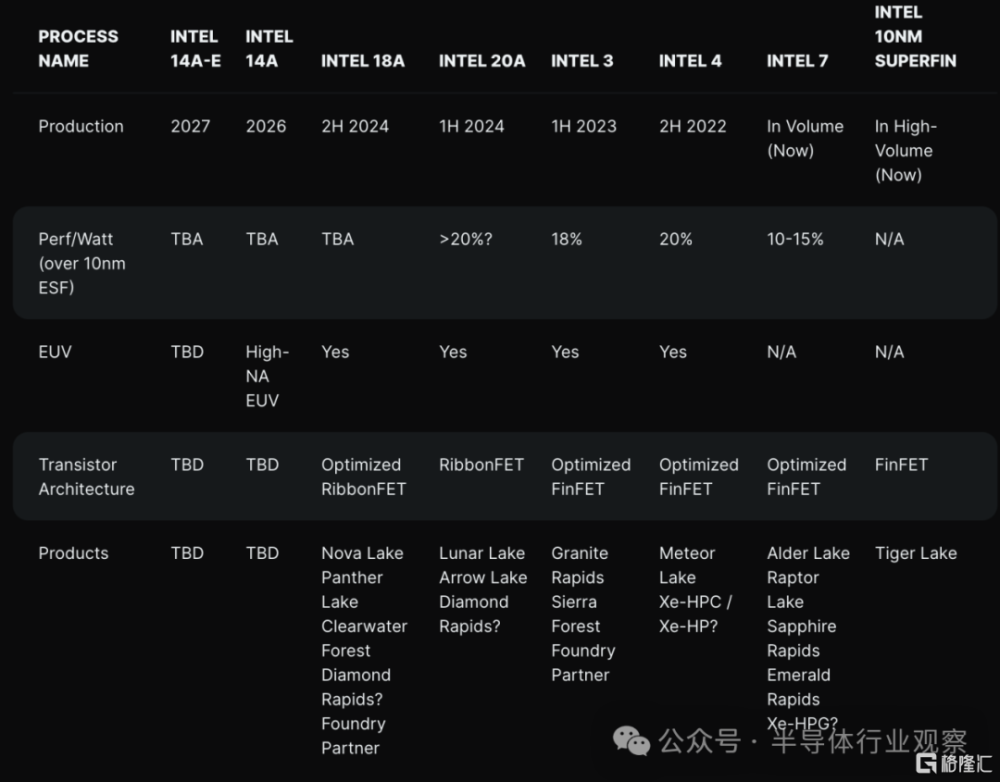

英特爾,信心滿滿

在先進工藝上落後了很多年的英特爾在2nm上面則信心滿滿。

Intel CEO Pat Gelsinger在去年年底接受採訪時表示,自家的18A制程(1.8nm)比領先台積電N2,在這塊他們2年內沒有對手。英特爾高級副總裁 Sanjay Natarajan更是 透露,該公司將通過 20A 工藝“引領小型化”,該工藝將於今年投入生產。

相關報道表示,該節點有望徹底改變 IFS 的產品組合和半導體行業。20A 節點預計將採用全新的 RibbonFET 晶體管,取代現有的 FinFET 架構。與此同時,該節點還將提供新的互連創新,即 PowerVia。

在五月的財報電話會議上 Pat Gelsinger重申,公司的第一代全柵極 (GAA) RibbonFET 工藝,即intel 20A,有望在今年推出。後續產品是intel 18A,他說,英特爾 18A 將於 2025 年上半年投入生產,產品也將在不久後上市。

作爲英特爾五年四代工藝的最後一個節點,英特爾 18A 工藝是該公司的分水嶺,人們對其寄予厚望。英特爾表示,這將使其多年來首次在性能上超越競爭對手,標志着英特爾重返半導體工程的頂峰。

具體到技術方面,據IEEE報道說,英特爾今年推出的 20A 工藝(先於 18A 工藝)爲芯片制造業帶來了主要特色之一,那就是背面供電。英特爾也將成爲第一家在商用芯片中引入背面供電的芯片制造商。根據英特爾去年夏天發布的數據顯示,僅背面供電一項就將性能提升了 6%。

英特爾 18A 工藝技術的背面供電網絡技術與英特爾 20A 芯片中的技術基本相同。然而,該技術在 Clearwater Forest 中得到了更大的利用。即將推出的 CPU 在基片內包含所謂的“片上電壓調節器”(on-die voltage regulator)。電壓調節器靠近其驅動的邏輯意味着邏輯可以運行得更快。距離越短,調節器就能更快地響應電流需求的變化,同時消耗更少的電量。

由於邏輯芯片採用背面供電,電壓調節器和邏輯芯片之間的連接電阻要低得多。同時,電源通孔技術以及 Foveros 堆疊爲英特爾提供了一種非常有效的連接方式。

除了背面電源之外,這家芯片制造商還利用英特爾 20A 工藝轉向了另一種晶體管架構:RibbonFET。RibbonFET 是一種納米片或全柵晶體管,它取代了FinFET(自 2011 年以來一直是 CMOS 的主力晶體管)。借助英特爾 18A,Clearwater Forest 的邏輯芯片將採用第二代 RibbonFET 工藝制造。據英特爾介紹,雖然這些器件本身與英特爾 20A 中推出的器件沒有太大區別,但器件的設計靈活性更高。

這種靈活性意味着標准單元(設計人員可用來構建系統的基本邏輯塊)可以包含具有不同屬性的晶體管。這使得英特爾能夠开發一個“增強庫”,其中包含比英特爾 20A 工藝更小、性能更好或更高效的標准單元。

據悉,英特爾的客戶已表示支持英特爾的系統代工服務,微軟董事長兼首席執行官薩蒂亞·納德拉在Intel Foundry Direct Connect大會上宣布,微軟計劃採用英特爾18A工藝制造由英特爾設計的芯片。

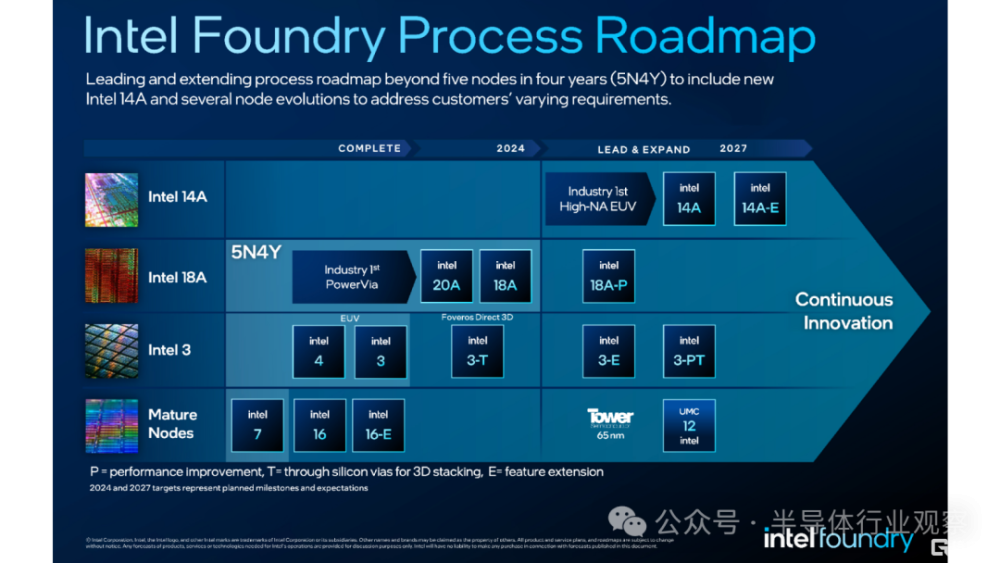

在英特爾的規劃中, 還有一個與其他兩個競爭對手不同的點,那就是他們率先採用ASML最新的High NA EUV光刻機。英特爾代也表示,公司已收到並組裝了業界首台高數值孔徑 (High NA) 極紫外 (EUV) 光刻系統。新工具能夠大幅提高下一代處理器的分辨率和功能擴展能力,使英特爾代工廠能夠在英特爾 18A 之後繼續保持工藝領先地位。

英特爾認爲,高數值孔徑 EUV 是 ASML 與英特爾數十年合作後开發的下一代光刻系統。作爲高數值孔徑 EUV 的先行者,英特爾代工廠將能夠在芯片制造中提供前所未有的精度和可擴展性。這反過來將使英特爾能夠开發具有最具創新特性和能力的芯片。

據透露,此台由ASML供應的TWINSCAN EXE:5000 High-NA EUV微影設備,將开始進行多項校准步驟,預計於2027年啓用、率先用於Intel 14A制程。

1nm,提前开打

如文章开頭所說,除了上述三家晶圓廠以外,日本Rapidus也正在成爲2nm工藝的新興力量。今年年初他們表示,公司位於北海道千歲市的2 nm芯片工廠興建工程順利,試產產线將按計劃在2025 年4 月啓用,且有信心能一步一步實現2027年量產的目標。

他們同時透露,公司有意研發1nm工藝。這個未來的工藝當然也成爲了三大晶圓廠的新目標。

據Business Korea報道,三星將在六月將公布其最新的技術路线圖,據報道,其 1nm 量產計劃從 2027 年提前到 2026 年。據稱,三星的SF1.4工藝將與台積電的1.4nm工藝競爭,原本計劃於2027年开始量產。現在,該公司似乎做出了更新,將計劃提前了。

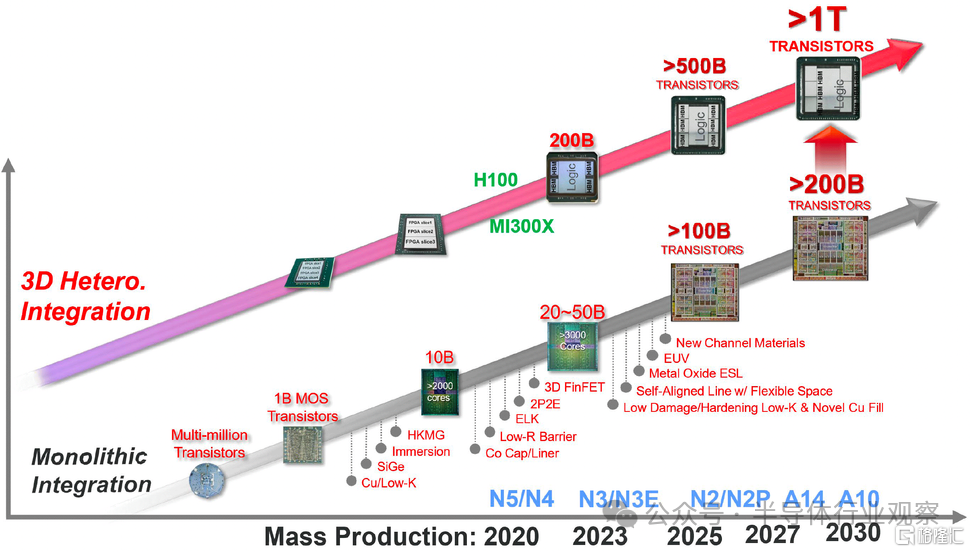

至於台積電方面,則計劃在2027年達到A14節點,並在2030年達到A10節點,即1nm制程芯片。屆時,採用台積電3D封裝技術的芯片晶體管數量將超過1萬億個,而採用傳統封裝技術的芯片晶體管數量將超過2000億個。

根據Intel 最新的路线圖,Intel 14A 提前至2026 年,並於2027 年增加新制程,即1 納米(Intel 10A)。不過,英特爾沒透露10A 節點任何細節,但至少有雙位數的功耗與性能改進。英特爾CEOPat Gelsinger 曾表示,新制程改善臨界值約14%~15%,因此10A 與14A 可能也會有這樣改進。

另據英特爾藍圖,Intel 14A 也於2027 年最佳化,故10A 似乎介於14A 和14A-E 之間。

但是,據 Volksstimme 報道,英特爾位於德國馬格德堡附近的 Fab 29 module 1 和module 2 的建設因歐盟補貼審批待定以及需要移除黑土以在其他地點重新使用而被推遲,新的時間表將开工時間推遲到 2025 年 5 月 。如果英特爾能夠快速完成建設和工具安裝,該工廠仍可能在 2027 年底至 2028 年初按時投產。但這對公司來說仍可能是一個問題。

最初,建設計劃於 2023 年上半年开始,但由於補貼延遲,建設被推遲到 2024 年夏天。現在又進一步推遲了。

按照規劃,英特爾的 Fab 29.1 和 Fab 29.2 計劃於 2027 年底开始運營,這意味着它們將採用非常特殊的制造工藝,例如 英特爾的 14A(1.4 納米)和 10A(1 納米)工藝節點。這些制造技術旨在用於制造英特爾路线圖中非常特殊的產品。

Fab 29.1 和 Fab 29.2 旨在生產計劃於 2028 年下半年推出的客戶端 PC 產品,所以盡管英特爾有時間提高產能,即使該工廠在 2028 年中期准備就緒,但時間安排將會非常緊張。然而,該報告描繪了一幅更加可怕的圖景,因爲它稱英特爾現在估計“建造這兩家工廠需要四到五年時間”,“因此將於 2029 年至 2030 年开始生產”

這也許會給英特爾的崛起帶來新的障礙。但考慮到他們在美國大本營和愛爾蘭以及以色列的多地布局,也許狀況並沒有想象中那么差。

標題:2nm,大战打響!

地址:https://www.iknowplus.com/post/112063.html