DRAM,下一步是什么?

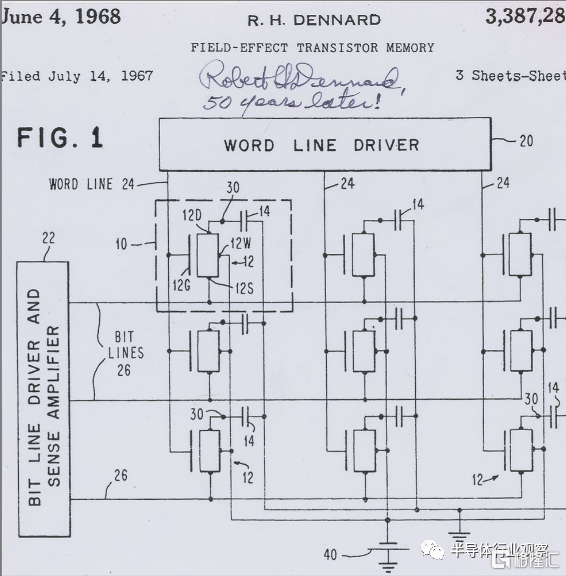

1968 年 6 月 4 日,Robert Dennard 獲得了單晶體管、單電容器 DRAM 單元設計理念的專利。這在今天聽起來並不驚天動地,但在六十年代,這是一種激進的新方法。

從1966年开始,Robert Dennard就試圖創建一種 SRAM 和磁芯存儲器的替代方案,前者都每個數據位都需要有 6 個 MOS 晶體管,或者需要一個半硬鐵氧體磁芯環。他觀察到 MOS 技術能夠構建電容器,從而得出結論:一個晶體管和一個電容器就足以構成存儲芯片。這種簡單的結構至今仍是 DRAM 的構建方式。

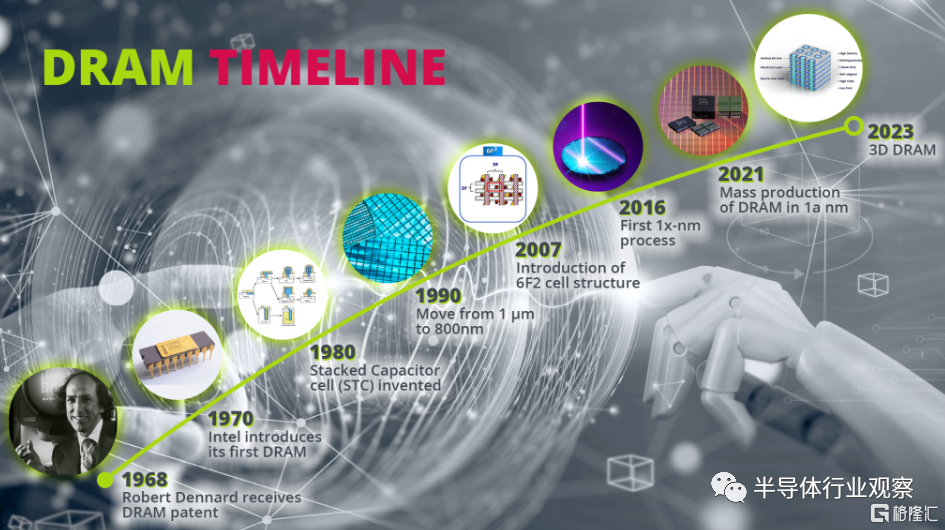

早在 1969 年,Advanced Memory System 就將其第一款 MOS DRAM 芯片商業化,但將 1024 位芯片出售給霍尼韋爾,而霍尼韋爾又要求英特爾基於其开發的三晶體管單元制造 DRAM。由於這款三晶體管1102 DRAM存在諸多問題,英特爾自行設計並於1970年10月推出了第一款i1103 DRAM,這是第一款商用且成功的DRAM IC。

DRAM 是如何工作的?

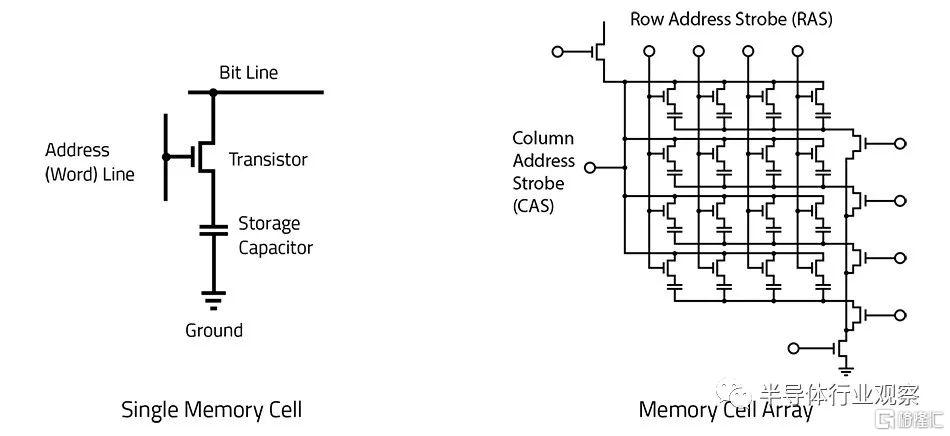

盡管1晶體管1電容的結構非常簡單,DRAM在發展初期也遇到了麻煩。事實上,英特爾推出的前五代 DRAM的良率非常低,因爲 DRAM 單元的模擬特性才剛剛开始顯現。雖然存儲單元本身包含數字信號(0或1),但爲了產生數字信號,必須讀出、放大並寫回模擬信號。爲了理解這意味着什么,讓我們看看 DRAM 結構。

DRAM 單元以規則的矩形、網格狀圖案布局,以便於通過字线和位线對其進行控制和訪問,並且需要感測放大器來讀取 DRAM 單元中包含的狀態。初始放大後,信號需要在芯片上快速長距離傳輸,再次需要第二次模擬傳感放大過程。當存取晶體管被激活時,電容器中的電荷與位线共享。位线的電容比電容器的電容大得多(大約十倍)。因此,位线電壓的變化是微小的。需要檢測放大器將電壓差分解爲邏輯信號系統指定的電平。這都是非常類似的行爲。

但最初的 DRAM 設計者必須解決的問題是連接和感測單元時的傳播延遲,這些問題需要以模擬方式精確計時,並考慮到最遠位置最慢的單元。如果時序不正確且太早或太短,信號可能會翻轉到錯誤的方向,或者寫回存儲單元的信號太弱。

經過幾位測試、設計和產品工程師的詳細分析才解決了這些問題,但在那之後,DRAM的成功故事就开始了。英特爾 i1103 也被稱爲“核心殺手”,因爲它非常成功地取代了傳統的基於鐵氧體核心的存儲單元。

縮放就是一切

當筆者在 20 世紀 80 年代末开始涉足半導體行業時,行業正在研究 5000 納米工藝的 DRAM。工作人員會打印出掩模,或者更確切地說,將它們繪制在箔片上,然後我們使用簡單的相機將它們縮小 100 倍。如今,我們採用 12 納米工藝,最輕微的污染都會影響蝕刻並破壞cell。

過去幾年我們所看到的規模擴張令人驚嘆。Intel 4004 處理器的運行頻率爲 740kHz,比當今的處理器和 DRAM 接口慢 200 萬倍。如今,我們擁有 16Gb 單芯片,比第一代 DRAM 多 1600 萬倍。

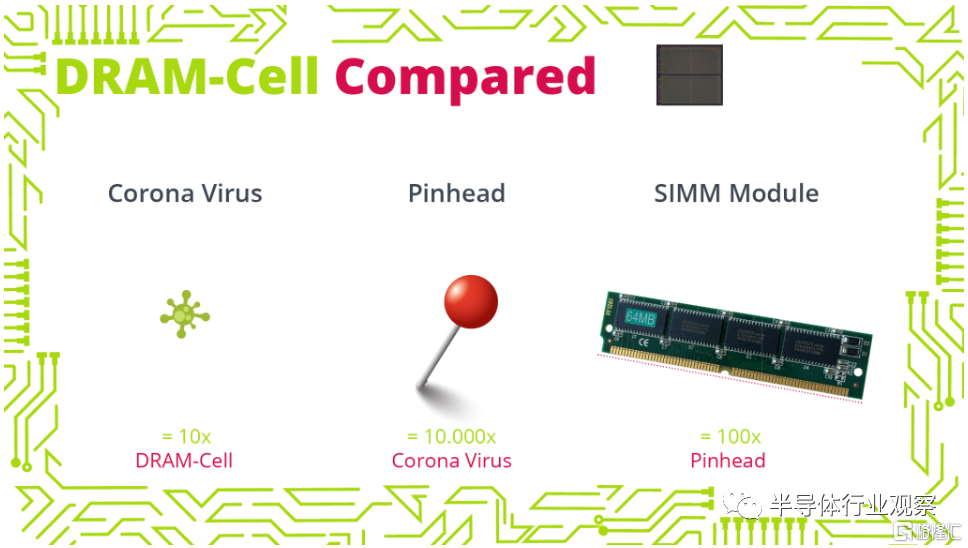

您是否知道,利用當今的處理節點,您可以將 10 個 DRAM 單元壓縮到 1 個冠狀病毒中?如今,存儲單元非常小,只能容納 10,000 個電子。它們是微小而精致的結構,必須被拉到粗糙的位线上來檢查它們的負載是 0 還是 1。考慮到這一點,它們能夠可靠地工作,而且 DRAM 和閃存大約佔全球所有半導體銷售的30%,這實際上是一個小奇跡。如今,它們在火星漫遊車、彗星着陸設備上運行多年,基本上成爲地球上所有電子設備的一部分。

現在,三星、SK海力士和美光也成爲全球領先的三大DRAM龍頭,他們把持着全球大部分的DRAM市場份額,他們的技術也進入到12nm的級別。

今年五月,三星宣布,其採用業界最先進的 12 納米 (nm) 級工藝技術的 16 Gb DDR5 DRAM 已开始量產。與上一代相比,三星全新 12 納米級 DDR5 DRAM 功耗降低高達 23%,同時晶圓產能提高高達 20%。其出色的能效使其成爲希望降低服務器和數據中心能耗和碳足跡的全球 IT 公司的理想解決方案。

三星 12 納米級工藝技術的开發之所以成爲可能,是因爲使用了有助於增加cell電容的新型高 κ 材料。高電容會導致數據信號中產生顯著的電勢差,從而更容易准確地區分它們。該公司在降低工作電壓和降低噪音方面的努力也有助於提供客戶所需的最佳解決方案。

三星的 12 納米級 DDR5 DRAM 系列擁有每秒 7.2 吉比特 (Gbps) 的最大速度,即可以在大約一秒內處理兩部 30GB 超高清電影的速度,將支持越來越多的應用,包括數據中心、人工智能和下一代計算。

與此同時,韓國的SK海力士也對外表示,公司已完成現有DRAM中最爲微細化的第五代10納米級(1b)技術研發,並將適用其技術的DDR5服務器DRAM提供於英特爾公司(Intel®)开始了“英特爾數據中心存儲器認證程序(The Intel Data Center Certified memory program)”。

據介紹,SK海力士向英特爾提供的DDR5 DRAM產品運行速度高達6.4Gbps(每秒6.4千兆比特),公司技術團隊實現了目前市面上DDR5 DRAM的最高速度。與DDR5 DRAM初期階段的試制品相比,數據處理速度提升了33%。

SK海力士進一步指出,公司在此次1b DDR5 DRAM上採用了“HKMG(High-K Metal Gate)”工藝,與1a DDR5 DRAM相比功耗減少了20%以上。

美光在去年11 月初則表示,公司正在向部分智能手機客戶運送其 1-beta DRAM 的合格樣品,並已做好大規模生產的准備。而在美光看來,公司的 1-beta DRAM 的推出標志着內存創新的又一次飛躍,這是其專有的多重圖案光刻技術與領先的工藝技術和先進材料能力相結合所帶來的。

美光科技透露,憑借業界首創的 1β 節點,公司可在更小的佔地面積內實現更高的內存容量,從而降低每比特數據的成本。DRAM 的擴展在很大程度上是通過每平方毫米半導體面積提供更多、更快的內存的能力來定義的,這需要縮小電路以在指甲蓋大小的芯片上容納數十億個存儲單元。對於每個工藝節點,半導體行業幾十年來每一兩年都會縮小器件尺寸。然而,隨着芯片變得越來越小,在晶圓上定義電路圖案需要挑战物理定律。

美光指出,1-Beta LPDDR5X 每芯片容量爲 16Gb,比上一代產品高出 35%,並且與上一代產品相比節能 15%。能獲得這樣的突破,是新節點在新工藝、材料和設備支持下取得的成果。未來,美光可以積極擴展存儲單元陣列的尺寸以及染料中其余電路的尺寸,以節省空間。

下一步是什么?

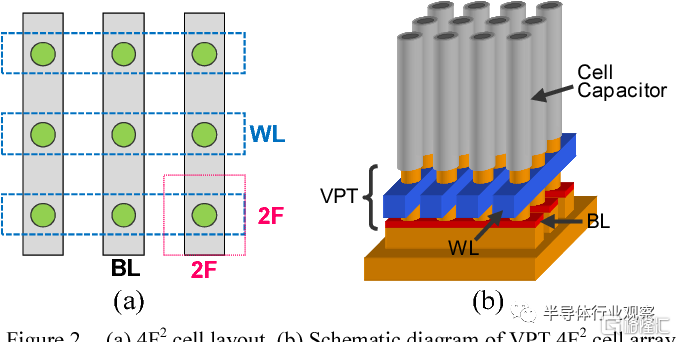

對於傳統DRAM未來的發展,如Techinsights所說,到目前爲止,我們已經看到了 8F2 和 6F2 DRAM Cell設計,其中 unit cell包括 1T(晶體管)和 1C(電容器)。這種 1T+1C 單元設計將用於未來幾代 DRAM 的 DRAM 單元設計。然而,由於工藝和布局的限制,DRAM 廠商一直在开發 4F2 單元結構,例如 1T DRAM 或無電容器 DRAM 原型,作爲下一個擴展 DRAM 技術的候選者之一。

對於10nm級及以下的DRAM單元設計,應該加入更多創新的工藝、材料和電路技術,包括High-NA的EUV、4F2、1T DRAM、柱狀電容器( pillar capacitor)、超薄更高k電容器電介質和低 -k ILD/IMD 材料。

此外,3D DRAM 被譽爲下一個重大事件。但從存儲晶體管器件的發展中面臨的挑战以及對超低泄漏 DRAM 要求的極端要求,我很難想象這種情況會在短期內發生。在過去30年裏,行業也一直在努力尋找堆疊解決方案。由於您正在處理多晶硅並且現在具有低泄漏或嚴格的浮動晶體管要求,因此在閃存中堆疊更容易。FLASH 原理只是基於捕獲電荷引起的閾值電壓變化。但在 DRAM 中,您需要具有完美低泄漏行爲且無浮動塊的單晶結構來完美切換存儲單元晶體管,因此 DRAM 可以以最小泄漏關閉,以將電荷保持 64 毫秒。

例如據韓媒TheElec獲悉,三星已經組建了一個團隊來开發 4F2 DRAM。消息人士稱,如果這家科技巨頭成功,與 6F2 DRAM 相比,它能夠將裸片表面減少 30%。

十年前,內存芯片制造商試圖將 4F2 商業化,但當時失敗了。但現在三星認爲,與競爭對手 SK 海力士和美光正在开發的 3D DRAM 相比,這種結構更容易實現。三星的目標是开始將 4F2 結構應用於 10 納米 (nm) 或以下節點制造的 DRAM,因爲它認爲從那時起它可以將通道長度縮小多少是有限的。

三星的 4F2 旨在讓晶體管垂直向上。它要從下到上放置源極、柵極、驅動器和電容器。連接字线和位线將使它們的尺寸分別爲2F和4F。這將是一個全新的結構。報道指出,在10nm以下,三星會推出一代4F2;下一代將使用直接粘合來制作 2 層。

雖然大家都在探索不同的路勁,但 3D DRAM 仍然在激勵工程師想出新的方法。

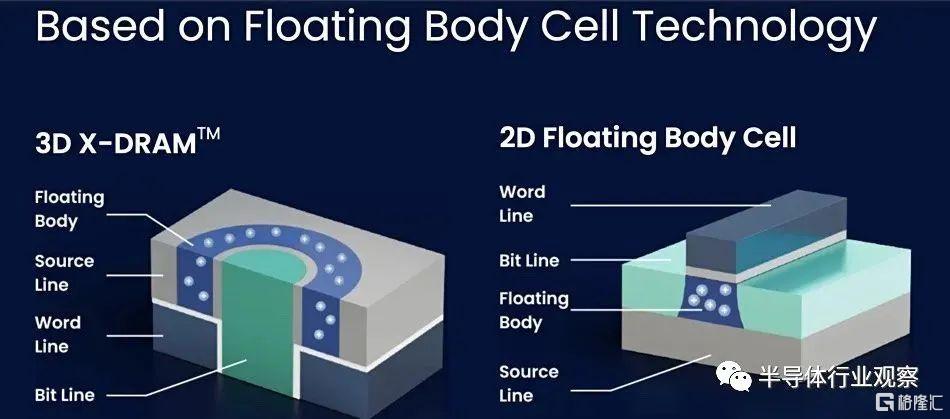

例如一家名爲NEO Semiconductor的初創公司認爲,它已經找到了一種方法,可以通過其 3D X-DRAM 技術實現這一目標。該概念具有基於無電容器浮體單元 (FBC) 技術的類 3D NAND DRAM 單元陣列結構。這種 FBC 技術使用一個晶體管和零個電容器將數據存儲爲電荷。NEO 表示它可以使用當前的 3D NAND 類工藝制造,並且只需要一個掩模來定義位线孔並在孔內形成單元結構。這提供了一種高速、高密度、低成本和高產量的制造解決方案,這是一個重要的主張。

不用很久的未來,相信 我們很快就會看到 3D DRAM 是否會取得突破。因爲畢竟過去的55年已經展現了DRAM無限的創新力量。

標題:DRAM,下一步是什么?

地址:https://www.iknowplus.com/post/7786.html