互聯,成爲核心技術

今年,人工智能毫無疑問是全球最火熱的技術,同時也成爲了半導體行業最炙手可熱的新市場。在人工智能技術中,目前看來影響力最大的技術將會是大模型技術,其核心特點就是通過使用規模巨大(參數可達百億到千億數量級)的模型,並且在海量的數據上訓練,來實現人工智能能力的突破,並且賦能新的應用,其中典型的例子就是去年下半年开始獲得萬衆關注的ChatGPT;而在未來,大模型的復雜度預計會進一步提升,以滿足應用的需求。

訓練和部署大模型需要強而有力的硬件支持,而這也是人工智能時代芯片成爲核心技術的原因,因爲大模型需要的算力歸根到底來自於芯片,同時人工智能市場的發展也極大地推動了芯片行業的市場規模,以及相關芯片技術的演進。

在給人工智能大模型提供足夠的算力用於訓練和部署的核心芯片技術中,數據互聯正在佔據越來越重要的位置。芯片互聯越來越重要主要出於兩個原因:

首先,隨着大模型的參數規模和訓練數據容量快速提升,訓練和部署最新的大模型一定會使用分布式計算,因爲單機幾乎不可能提供運行大模型的足夠算力。在分布式計算中,隨着分布式計算節點數量提升,理想情況下計算能力是隨着計算節點數量线性提升,但是現實中由於不同計算節點間的數據交互需要額外的开銷,因此只能接近而無法真正實現計算能力隨着計算節點增加而线性增加。換句話說,隨着模型規模越來越大,需要的分布式節點數量越來越多,對於這類分布式計算節點間的數據互聯需求(帶寬,延遲,成本等)也就越來越高,否則這類分布式計算中的數據互聯將會成爲整體計算中的效率瓶頸。

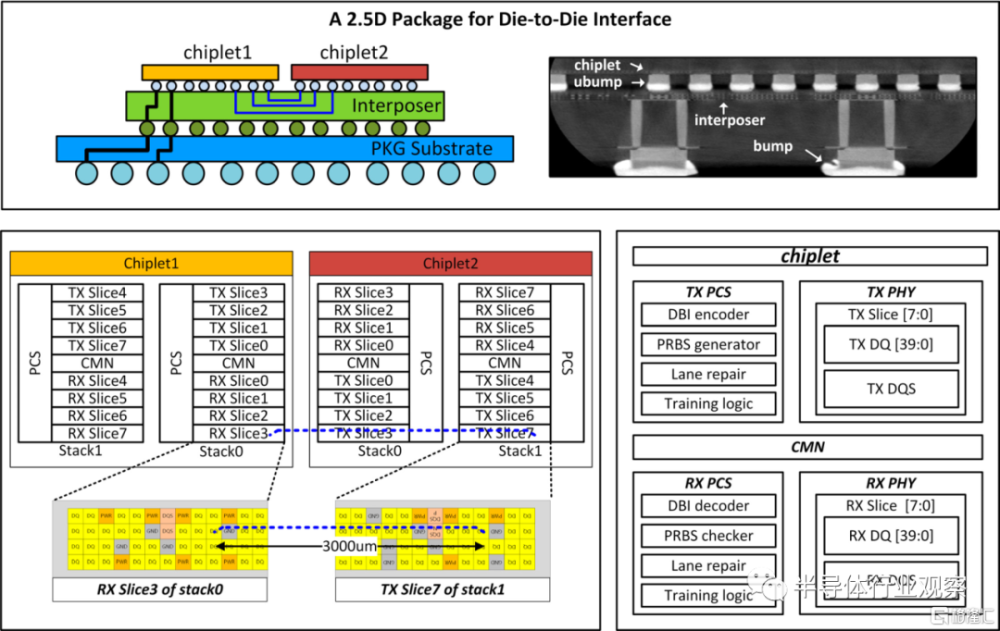

其次,從芯片層面考慮,隨着摩爾定律越來越接近物理極限,目前以chiplet(芯片粒)爲代表的高級封裝技術正在成爲芯片性能提升的重要方式。使用chiplet可以把單個復雜的大芯片系統分成多個小的芯片粒,每個芯片粒都可以用最合適的工藝去單獨制造,因此確保復雜的芯片系統可以以合理的成本和良率來制造。對於人工智能大模型而言,用於訓練和部署的芯片的規模都非常大,因此chiplet將會成爲支持人工智能芯片的核心技術。而在chiplet方案中,多個chiplet之間的數據通信也需要數據互聯技術,換句話說高帶寬、高密度的數據互聯將會成爲使用chiplet搭建的人工智能加速芯片中的核心組件。

如上所述,在人工智能時代,數據互聯將會成爲核心技術,而其中最關鍵同時也是未來將會有最多發展的數據互聯方案,就是用於分布式計算中的中長距離數據互聯,以及用於chiplet場景中的超短距離數據互聯。

用於分布式計算的數據互聯:硅光子技術成爲關鍵

人工智能大模型的分布式計算,包括訓練和部署,通常都在數據中心中完成。我們在數據中心數據互聯中看到兩個重要趨勢,即常規長距離通信的進一步規模化,以及新的短距離應用的崛起。

在常規的長距離數據中心數據互聯領域,目前爲了滿足人工智能等應用的需求,互聯速度正在快速提升,從今天主流的100/200/400Gbps光互聯技術快速進展到800Gbps光互聯技術,而到2026年更是預期會使用上1.6Tbps光數據互聯。除了數據率提升之外,在人工智能時代,數據中心中每台服務器上對於數據互聯的需求也在提升,因此單台服務器會需要更多的光數據互聯模塊。與傳統的分立式光互聯模塊相比,基於硅光技術的光互聯模塊能實現更高的集成度:在硅光技術中,波導器件、光柵和調制器等核心模塊都可以集成在同一塊芯片上,從而可以大大降低光互聯模塊的成本,這對於人工智能應用來說是一個重要優勢,因爲訓練大模型中需要大量的高帶寬數據互聯同時也不能提高太多成本。

隨着對於數據互聯帶寬的要求進一步提升,數據中心中的光互聯帶寬也需要進一步提升,功耗則需要進一步降低,而從這個角度,硅光子技術搭配共封裝光學(co-packaged optics,CPO)也會成爲下一代光互聯帶寬和功耗優化的核心技術。

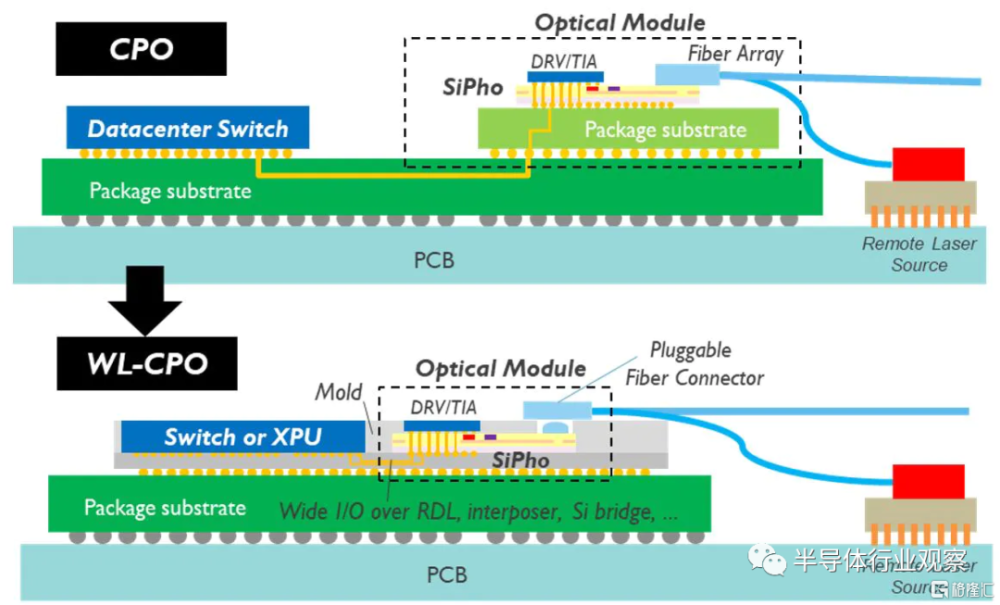

在共封裝光學技術中,使用硅光子技術實現的光互聯模塊和使用傳統CMOS技術實現的數字邏輯(例如光互聯模塊後接的網絡模塊)將會使用高級封裝技術集成在同一個封裝裏——而在傳統的實現中,光互聯模塊和其他CMOS芯片並不會集成在同一個封裝裏。通過使用共封裝光學技術,光互聯模塊和其他芯片之間的互聯距離大大縮小,從而減小了光互聯模塊與電信號接口的信號傳輸衰減,而這對於超高帶寬通信至關重要,因爲在這些超高數據率的應用中,真正限制數據率的往往不是光信號,而是光信號在轉換成電信號之後的信號衰減(即last-mile問題)。另一方面,通過減小信號衰減,光互聯模塊的整體功耗可以減小。而共封裝光學是基於硅光技術之上的,因爲傳統的分立式光模塊因爲體積太大,無法使用共封裝光技術和其他芯片集成到同一個封裝裏。

除了目前已經爲人熟知的數據中心中長距離光互聯模塊之外,在人工智能時代將會崛起的另一個光互聯技術將是計算集群中的中短距離光互聯。如前所述,在大模型時代,分布式計算將會得到廣泛應用,而在具體的大規模分布式計算拓撲結構中,常用的結構就是首先由物理位置相鄰的服務器組成一個集群(cluster),在這樣的計算集群中執行需要大量數據交換的任務,而計算集群之間再使用長距離數據互聯連接在一起以提升計算規模。在這樣的計算集群中,目前常規的數據互聯是使用銅絞线的互聯;但是隨着對於數據帶寬、延遲和功耗的需求越來越高,使用在計算集群中的光互聯正在成爲越來越重要的技術路徑。

與長距離通信不同,計算集群間的數據互聯需要延遲極低、功耗也較低,但是由於互聯距離較小(即色散效應較小)因此可以允許更多的波分復用,因此光互聯可以考慮多個波分復用信道,每個信道的數據率較小(例如16-64Gbps),這樣做可以盡可能減小對於數字矯正技術的依賴(使用數字矯正技術將會提升延遲,同時也增加功耗),以滿足對於功耗和延遲的需求。此外,在計算集群中,我們會預期光模塊和CMOS芯片(例如GPU或者HBM)更緊密地集成在一起,因此在共封裝光學CPO技術之上,我們可能會看到集成度更高的晶圓級共封裝光學(WL-CPO)技術,該技術可以爲光學互聯模塊和CMOS芯片之間提供更多互聯接口,從而進一步增加通信帶寬。

用於chiplet的超短距離數據互聯

除了長距離光互連之外,另一個人工智能時代的重要數據互聯技術是用於chiplet之間通信的超短距離數據互聯。

隨着摩爾定律接近物理極限,使用chiplet來實現復雜芯片系統已經是業界共識。在人工智能時代,隨着對算力需求的進一步提升,單芯片系統預計會用到越來越多的chiplet,同時chiplet之間的互相通信需求也會越來越大。長距離光通信數據互聯的主要演進方向是共封裝光學這類的新封裝工藝,而與之相對地超短距離chiplet數據互聯演進更多是依賴電路設計和系統設計。我們可以看到chiplet對於數據互聯需求的兩大方向:

1、更高的數據帶寬,更長的通信距離(從毫米級別上升到釐米級別),更嚴格的功耗要求

2、更復雜的通信協議需求

先看第一個方向,這條需求對於chiplet數據互聯的電路設計提出了越來越多的需求。隨着chiplet數量越來越多,系統越來越復雜,勢必chiplet之間的互連距離會越來越長,這也就意味着互聯线上的衰減會更大,會需要更強的收發機;另一方面,隨着人工智能對於chiplet間數據通信帶寬的要求提升,每個chiplet上的數據互聯模塊數量也會增加,這就意味着單個數據互聯模塊的功耗不能過大以滿足總功耗的限制。另外,隨着數據互聯需求的快速提升,單個數據互聯模塊的芯片面積又不能太大,這樣才能滿足chiplet上總互聯接口的需求。因此,chiplet數據互聯電路主要有兩大指標,一個是能效比(J/bit),用來衡量數據率與功耗之間的關系;另一個指標則是數據率密度(bit/s/mm),用來衡量數據率與芯片面積之間的關系。隨着chiplet數據互聯需求的提升,未來我們可望會看到越來越高的數據率密度,同時越來越好的能效比。

第二個方向則是通信協議需求,這裏涉及了chiplet之間協同工作的方式,例如在處理器系統中,如何確保chiplet之間緩存一致性的問題。未來隨着chiplet系統越來越復雜,傳輸的復雜度也會提升,未來甚至可能會把目前NoC的模式搬到chiplet上。這對於chiplet數據互聯IP的設計也是一個新的發展方向。

總體來說,對於chiplet的數據互聯來說,隨着人工智能相關需求的興起,未來它可望會成爲芯片IP領域一個越來越重要的品類,而具體的技術方向,則會沿着電路設計的優化和系統/傳輸協議復雜度提升的方向去演進。

標題:互聯,成爲核心技術

地址:https://www.iknowplus.com/post/36000.html