FD-SOI,卷土重來

如今談起晶圓工藝,大家提及的往往是日趨成熟的Fin-FET,抑或是尚出於完善階段的GAA,台積電、三星、英特爾……無數廠商都在爲了這兩種工藝前後奔忙,不過卻鮮少有人知曉另一種與Fin-FET齊名的工藝。

2000年,著名的“FinFET”之父胡正明在美國加州大學領導了一個研究小組,當時大家已經對摩爾定律的未來感到悲觀,而他們的研究目標就是再續摩爾定律,讓CMOS技術拓展到25nm及以下領域。

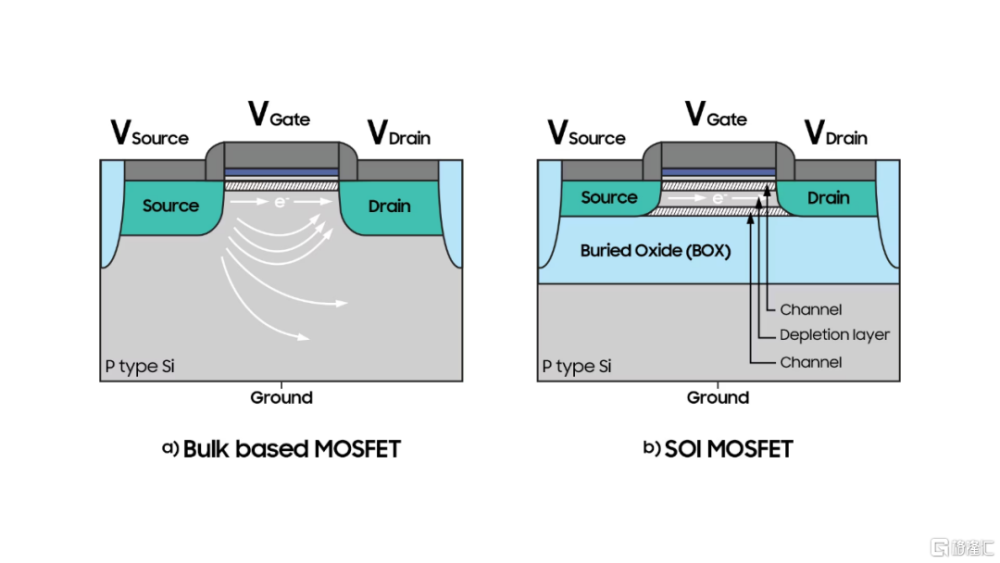

當時的研究發現,當柵極長度逼近20nm大關時,對電流控制能力急劇下降,漏電率相應提高,傳統的平面MOSFET結構中,不再適用舊技術,到2010年時,Bulk CMOS(體硅)工藝技術會在20nm走到盡頭。

胡正明在當時想到了兩種解決方法,其中一種方法是將窄通道像鯊魚鰭一樣在基片上方垂直延伸,柵極可以三面環繞通道,而不是僅在通道上方,從而讓柵極更好地控制電荷的流動。這種結構被稱爲FinFET。

而另一種想法卻截然不同,是在晶體管下面的硅中埋入一絕緣層,使電荷難以溜過柵極。這種設計後來被稱爲全耗盡絕緣體上硅FD-SOI(fully depleted silicon-on-insulator)。

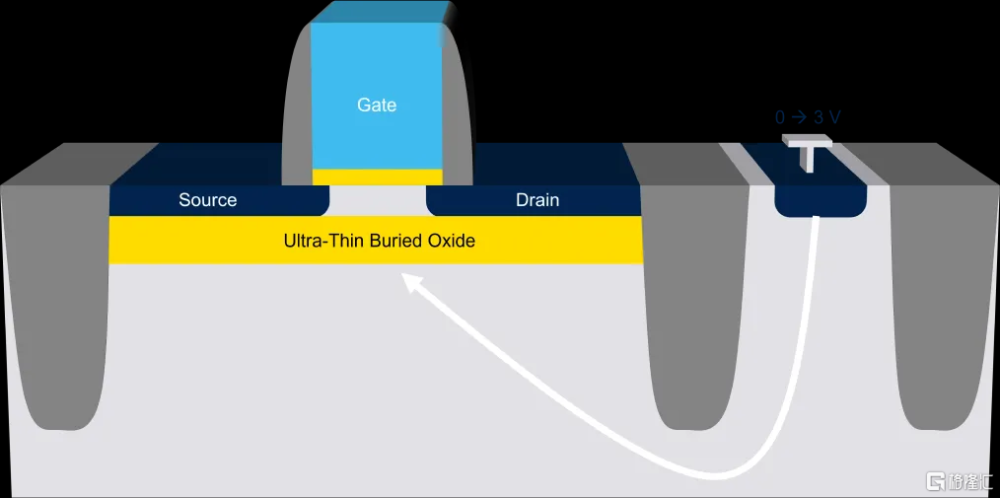

這項技術主要依賴於兩項技術創新。首先,在襯底上面制作一個超薄的埋氧層。然後,用一個非常薄的硅膜制作晶體管溝道。因爲溝道非常薄,無需對通道進行摻雜工序,耗盡層充滿整個溝道區,即全耗盡型晶體管。

從結構上看,FD-SOI晶體管的靜電特性優於傳統體硅技術。埋氧層可以降低源極和漏極之間的寄生電容,還能有效地抑制電子從源極流向漏極,從而大幅降低導致性能下降的漏電流。由於FD-SOI晶體管結構及其超薄絕緣層,偏置電路的效率更高。而且,埋氧層的存在允許施加更高的偏置電壓,使晶體管動態控制取得突破性進步。

2011年,英特爾推出其第一代FinFET工藝產品——22nm的Ive Bridge處理器,2013年11月,台積電成功試產16nm FinFET,同時期的FD-SOI卻還停留在相對小衆的階段。

不過,隨着制程工藝的不斷迭代,FD-SOI在近兩年又成爲了大家的焦點,甚至還屢屢登上了半導體新聞的版面,到底是誰帶火了這項工藝呢 ?

受益於物聯網的FD-SOI

早期的 FD-SOI 技術缺少商用的FD-SOI 襯底,直到2006 年 Soitec 研發出滿足商用的高質量 FD-SOI 襯底之後,意法半導體聯合 Leti、Soitec 开發出基於 28nm 節點的 FD-SOI 晶體管,實現了真正的 FD-SOI 器件的制備。

不過雖然取得了一定的關鍵技術突破,但沒有出現具有市場競爭力的產品,代表性的僅是 Oki Electric 採用 FD-SOI 技術开發出用於低功耗手表的微控制器,但在2007 年 SOI 聯盟成立後,也有越來越多公司選擇FD-SOI 技術,开始逐步走向商業化的道路。

而近兩年物聯網市場的火熱,也爲FD-SOI催生出了更多應用機會。

事實上,即使在摩爾定律近年受到壓力之前,數字的擴展效益也往往優於模擬,新的結構往往會引入寄生效應和工藝變化,從而增加模擬設計人員的難度,而這種情況在塊狀 CMOS 中尤爲明顯,通常被歸類爲 SCE(短溝道效應)。

當今的 SoC 設計大多是數字設計,因此模擬設計人員和模擬 IP 提供商必須採用對數字 客戶最有意義的工藝進行設計,截至目前,Bulk CMOS 仍是當今的主流工藝,歷來是低成本的選擇,而突然轉到FinFET 技術上,不僅是技術挑战,也是一項經濟挑战,對於生命周期較短、產量較小的產品來說,成本已經高昂到難以承受的地步。

而物聯網市場的出現开闢了一系列大型垂直市場——消費、工業、醫療、智能家居和可穿戴設備,新一代物聯網產品需要將上市時間、低功耗、片上閃存、互連 IO 和射頻/模擬進行適當組合,與FinFET 相比,FD-SOI 提供了實現更高性能、更低功耗、更低成本的組合,更加經濟實惠的它开始受到重視,重新出現在了大家的視线當中。

回顧2016年,面對研發和資本投入成本呈指數級別增長的情況,衆多代工廠的客戶群正在面臨一場重大抉擇。當時,衆多Fabless公司都表示採用FinFET技術的成本太高,而且模擬和混合信號設計不太需要FinFET。

作爲參照,彼時的16nm/14nm芯片的平均設計成本約爲8000萬美元,而28nm平面技術(以Bulk CMOS爲代表)的平均設計成本爲3000萬美元。

美國類芯片設計公司 Sigma Designs當時表示,綜合考慮到產品的性能、功耗、上市周期等等,他們不會走FinFET路线。對於很多主打物聯網和射頻芯片的公司來講,28nm成爲了當時性價比最高的开發平台。

如此看來,FD-SOI有望承接FinFET拱手讓出的龐大市場,不過盡管格芯聯手ST,NXP等大力發展這項技術,還拉攏了三星、索尼、瑞薩等作爲盟友,但在28nm工藝節點上,台積電在生態圈和技術成熟度上的優勢實在太大,這也導致了FD-SOI在成本控制上依舊不夠理想。

簡單來講,沒有足夠的生產規模,導致原本的成本優勢被消弭,尤其是在台積電推出了28ULP CMOS低功耗技術後,用FD-SOI能做的,台積電不用FD-SOI也能做得到,價格反而更具優勢,這一點對於採用FD-SOI技術的廠商來說尤爲致命。

但展望未來,越來越多的廠商开始支持FD-SOI,一旦形成集群效應,不止是28nm和22nm這樣的成熟,下探至10nm都會具備一定的成本優勢,而物聯網市場也能受益於此,用更低功耗的芯片完成更復雜的工作。

FD-SOI技術的優越性

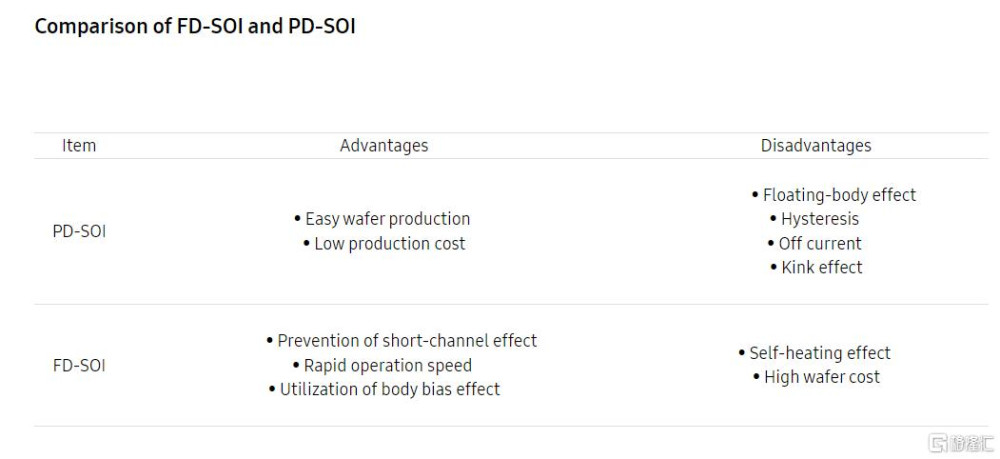

目前,SOI技術根據埋氧化層 (BOX) 的厚度和溝道單晶硅的厚度分爲兩種類型:部分耗盡型 SOI (PD-SOI) 和完全耗盡型 SOI (FD-SOI),我們可以從三星電子的一篇技術文章分析中一瞥這兩種SOI類型的優劣之初。

PD-SOI 即傳統的SOI技術,適用於功率器件等模擬產品,溝道的單晶硅厚度在 50nm-100nm 之間,BOX 的厚度在 100-200nm 之間,與體型晶體管相比,它的優點是能阻斷通過結點的漏電流,同時還能減少源極、漏極和本體之間產生的電容。

但PD-SOI的劣勢也相當明顯,基底上沒有施加電壓,因此會產生浮體效應。電子向漏極移動,但熱載流子效應產生的空穴卻無處可去,只能積聚在溝道硅中。這就導致在溝道硅上施加正電壓,從而產生磁滯現象--鐵磁材料的磁化滯後於磁場的變化--與初始運行前的狀態相比,器件運行後的特性發生了變化。此外,當累積的空穴數量達到一定水平時,正電壓會降低器件的閾值電壓(Vth),導致器件關斷時的關斷電流增大,當漏極電流從 Vth 降低處突然增大時,就會產生扭結效應。

而FD-SOI相較於PD-SOI來說,它的結構種具有超薄的溝道硅,被稱爲超薄體 (UTB) SOI,主體厚度約爲 10 納米,BOX 厚度爲 20-25 納米。溝道硅的薄度使其成爲全耗盡器件(FDD)成爲可能,從而形成一個完全耗盡的電荷層。

在 FDD 中,柵極對溝道的控制能力更強,可以減少短溝道效應,即隨着源極和漏極之間的距離減小,溝道中的漏電流會增大。一般來說,FDD 的關鍵方法是減少溝道硅的厚度。也有類似的技術,例如鰭式場效應晶體管(FinFET)或全柵極(GAA),但由於其三維結構,復雜性較高,而 FD-SOI 具有二維平面結構,技術難度相對較小,可以更快推出。

而Vth 是柵極上的電壓,用於开啓晶體管,因此高 Vth 需要更大的柵極電壓才能保持器件开啓,而低 Vth 則會導致溝道漏電流在不完全關斷狀態下流動。這就是將 Vth 保持在合理水平的原因。

FD-SOI的優勢也正在於此,柵極對溝道的更好控制,從而減少短溝道效應,最終無需摻雜來彌補 Vth 值的下降,或者至少可以將摻雜濃度降至較低水平。這可以提高載流子的遷移率,因爲載流子和雜質之間的散射(由於摻雜)被阻止了,它還能減少隨着雜質數量的增加而出現的隨機摻雜波動引起的 Vth 波動。

不過,FD-SOI 目前確實存在自熱效應的限制。由於用於絕緣的 BOX 是一種極好的絕緣體(SiO2),因此很難將運行過程中產生的熱量散發出去。因此,本體溫度會升高,器件的遷移率會降低,從而導致溝道電流減小。

總體來說,FD-SOI很好地解決了PD-SOI之中存在的既有問題,且由於是平面工藝,不需要花費更多成本來進行遷移,是未來功率半導體向前發展的最合適選擇之一。

那些FD-SOI廠商

首先需要明確的是,目前全球有三家公司具備FD-SOI代工能力,分別是意法半導體、三星和格芯。

先來說意法半導體,2012年,意法半導體宣布其克羅勒工廠已經具備28nm FD-SOI制程量產能力,是首個商業化代工FD-SOI的公司,其分別於2012年和2014年將FDSOI工藝授權給格芯和三星。

2018年,意法半導體宣布選定格芯22nm FD-SOI技術平台,採用格芯可量產的22FDX工藝和生態系統,爲未來智能系統提供第二代FD-SOI解決方案,與格芯在FD-SOI技術的發展上基本達成了一致。

再來說GF格芯,作爲FD-SOI制造技術的推動者,獲得意法半導體授權後,2017年在原來的基礎上發布了22 nm FD-SOI代工平台,截至2020年年底已實現營收45 億美元,交付芯片超過3.5 億顆。

2018年,格芯投產12 nm FD-SOI代工平台,該平台生產的產品幾乎擁有10 nm FinFET 工藝產品同等的性能,功耗和生產成本比16 nm FinFET工藝產品還低,需要注意的是,格芯曾宣布將獨立开發7nm制程FD-SOI技術,但之前已宣布正式放棄。

值得一提的是,在去年7月,ST和GF聯合宣布,雙方將在法國克羅爾現有的意法半導體 300 毫米工廠附近創建一家新的聯合運營的 300 毫米半導體制造工廠。該工廠的目標是到 2026 年全面提高產能,全面擴建時每年生產 620,000 片 300 毫米晶圓(約 42% ST 和約 58% GF)。按照他們在公告中所說,這個新設施將支持多種技術,特別是基於 FD-SOI 的技術,並將涵蓋多種變體。其中包括格芯市場領先的 FDX 技術和意法半導體低至 18 納米的綜合技術路线圖,預計在未來幾十年內,汽車、物聯網和移動應用對這些技術的需求仍然很高。

“我們的客戶正在尋求廣泛訪問 22FDX 汽車和工業應用的能力。新工廠將包括 GF 專用代工產能,爲我們的客戶提供 GF 的獨特創新,並將由 GF 人員進行現場管理。此次聯合運營的新制造產能擴張利用了意法半導體克羅爾斯現有的設施基礎設施,使格芯能夠加速我們的增長,同時受益於規模經濟,以高度資本效率的方式在我們差異化的 22FDX 平台上提供額外的產能,該平台已出貨超過 10 億顆芯片。通過這個合作,我們將擴大格芯在歐洲動態技術生態系統中的影響力,並鞏固我們作爲歐洲領先半導體代工廠的地位。”格芯首席執行官 Thomas Caulfield 博士說道。

最後是三星,2014年,三星與意法半導體籤訂28nm FD-SOI技術多資源制造全方位合作協議,授權三星在芯片量產中利用意法半導體的FD-SOI技術。同年,三星成功量產8Mb eMRAM,並利用28nm FD-SOI,在2019年成功量產首款商用eMRAM。

2019年,在三星推出首款商用eMRAM的同時即表示,MCU將是eMRAM的主要應用方向之一,未來將繼續擴大其嵌入式非易失性內存產品,其中包括1gb eMRAM測試芯片,並計劃使用其18FDS工藝制造eMRAM,以及更先進的基於FinFET的節點。

雖然格芯放棄了7nm FD-SOI,但歐洲尤其是法國並不想放棄這項目前自身尚處於領先地位的技術。

此外,據報道,法國CEA-Leti正計劃新建一條工藝引導线,基於全耗盡絕緣體上硅(FD-SOI)技術开發10納米低功耗工藝技術模塊,該技術未來將進一步向7納米拓展。該機構透露,FD-SOI新一代工藝將與18、22和28nm的現有設計兼容,並且還將包括嵌入式非易失性存儲器(eNVM)工藝,該項目由法國政府獨立於《歐盟芯片法案》提供資金。

在這些廠商的推動下,FD-SOI,迎來了新的契機。

標題:FD-SOI,卷土重來

地址:https://www.iknowplus.com/post/16314.html