台積電“攻防战”

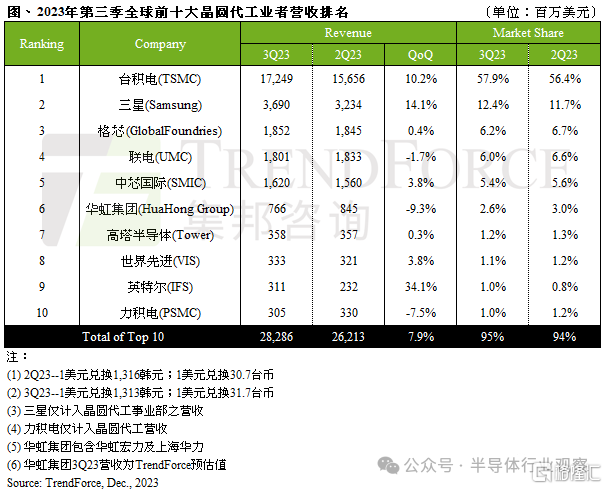

根據TrendForce發布的2023年第三季全球前十大晶圓代工排名來看,台積電依然佔據絕對優勢,保持着晶圓代工領域的全球霸主地位,穩坐行業頭把交椅。

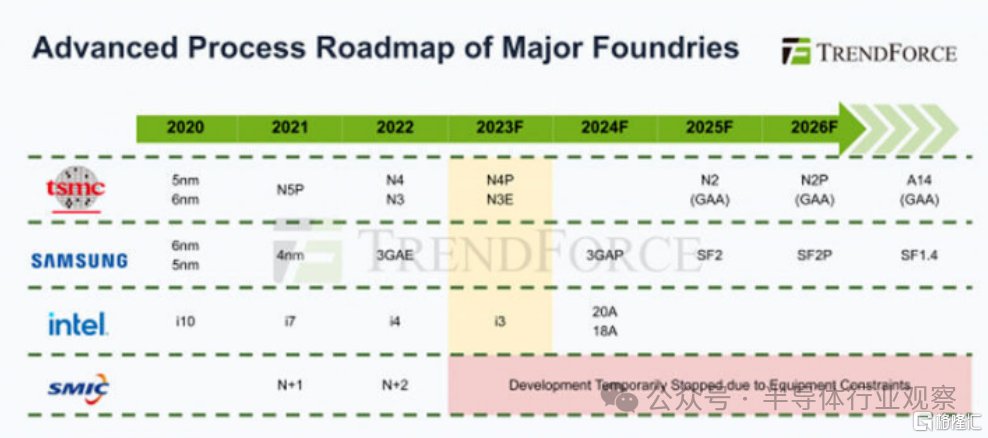

長期以來,在摩爾定律的驅動下,晶圓廠一直緊追先進工藝,這場決賽的最後僅剩台積電、三星和英特爾,在先進制程節點展开肉搏。

如今,隨着AI、高性能計算等新興技術的驅動,晶圓代工產業先進制程的重要性日益凸顯。據業界預測,全球芯片制造產能中,10nm以下制程佔比將會大幅提升,將由2021年的16%上升至2024年近30%。

更先進的芯片能撬動巨大的利潤空間。在此趨勢下,晶圓代工巨頭將面臨怎樣的起伏?台積電會因此繼續“封神”嗎?多面出擊的三星和英特爾,又將分得幾杯羹?

在這場晶圓代工行業的反擊和保衛战中,代工三巨頭動作頻頻。

三星、英特爾“攻城”

三星祭出“三板斧”

早在2019年,三星提出“半導體愿景2030”,就定下來未來10年內超越台積電的目標。爲了實現這一目標,近年來可謂大刀闊斧的向前跨越。

種種舉動在顯現出三星大張旗鼓的雄心之外,一個貫穿其中的信號仍在印證代工業的制勝之道:先進工藝、良率與客戶。這也是追趕台積電的必經之路。

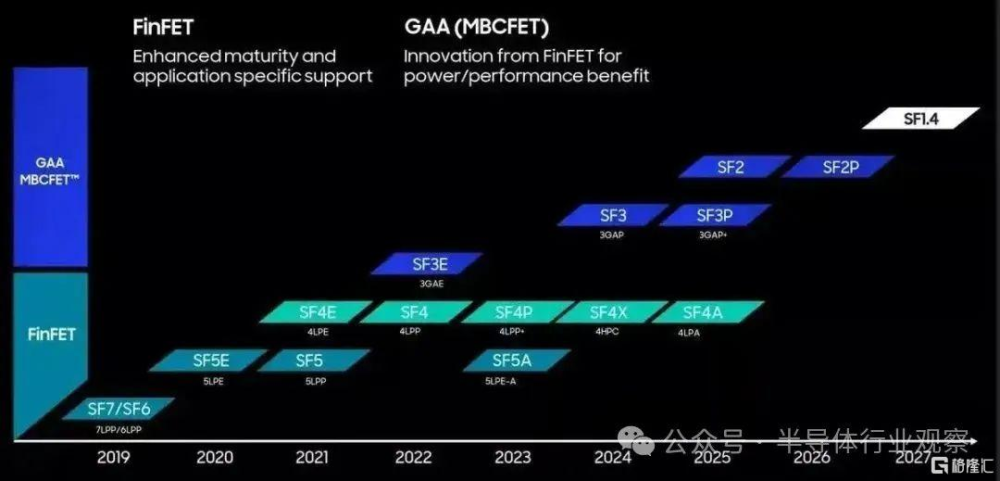

率先轉向3nm GAA

在先進制程領域,三星相比台積電總是棋差一招。例如,三星7nm量產之後,台積電宣布5nm量產,三星5nm量產之後台積電又宣布4nm試產,總是跟不上台積電的步伐。

直到3nm節點,三星看到了追趕的機會。

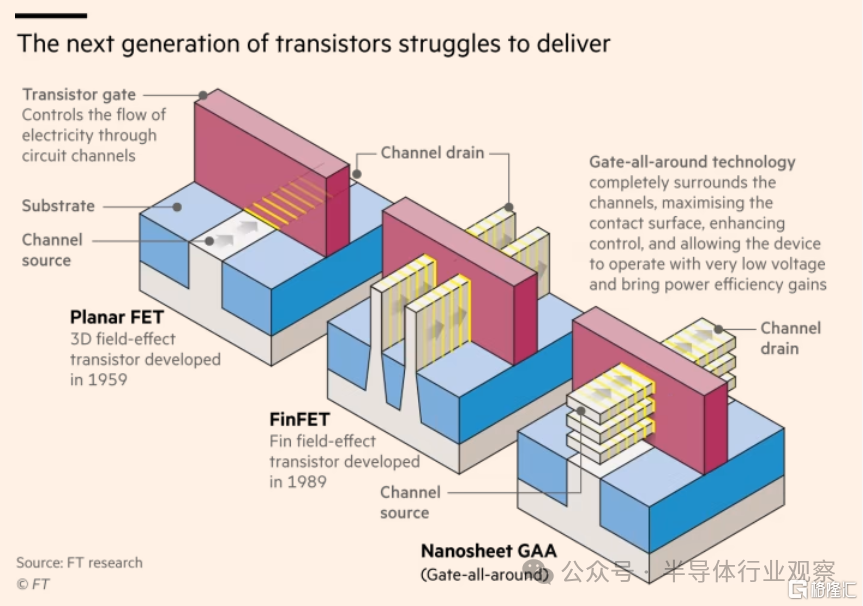

2022年6月,三星率先採用全環繞柵極GAA晶體管架構,發布了第一代3nm工藝,領先台積電量產,成爲全球首個量產3nm的代工廠。

GAA架構相較於傳統的FinFET架構,在性能、功耗和集成度等方面具有顯著優勢,被認爲是未來半導體技術的重要發展方向。

據介紹,與5nm工藝相比,三星第一代3nm GAA芯片可以降低45%功耗、性能提升23%、芯片面積減少16%。

三星先於其他公司採用了3nm工藝的GAA架構,但似乎正面臨良率低等問題。

有分析師警告說,雖然三星是第一家將3nm GAA芯片推向市場的公司,但它一直在努力解決“良率”問題。據接近三星的人士透露,其最簡單的3nm芯片的良率僅爲60%,遠低於客戶預期,並且在生產相當於蘋果A17 Pro或Nvidia圖形處理單元等更復雜的芯片時,良率可能會進一步下降。

良率問題直接影響了三星的訂單,使用者寥寥。

前不久,三星電子向投資者透露,將過渡和推進光刻技術,計劃2024年下半年向市場推出採用第二代3nm工藝技術(SF3)以及量產版4nm工藝(SF4X)的產品,進一步增強技術競爭力。

圖源:SevenTech

據韓媒《朝鮮日報》報道,三星電子已經着手制造第二代3nm制程的試制品,正在對SF3試制芯片進行性能和可靠性測試,並計劃在六個月內將良率提升至60%以上。

這一動作表明,三星正全力以赴爭奪客戶,與台積電展开激烈的競爭。

如果SF3的產量、性能和良率能夠保持穩定,並提供優惠價,原本轉向台積電的客戶可能會有機會回流,其中包括與高通的合作,力圖打破高通下一代5G旗艦芯片可能由台積電獨家代工的局面。此外,英偉達的H200、B100和AMD的MI300X等產品也可能採用三星的3nm制程。

同時,三星自己可以消化一部分產能,其綜合成本相對於台積電來說要更低,對於行業客戶來說,三星是芯片廠商的另一個選擇。

此外,三星還公布了2nm工藝量產的詳細計劃以及性能水平,計劃2025年實現應用在移動領域2nm工藝的量產,於2026和2027分別擴展到HPC及汽車電子。此外,據報道三星正准備確保下一代High-NA EUV光刻機的產量,預計這款設備將於2023年晚時推出原型,明年正式供貨。

降價搶客戶

近日,三星傳出本季調降晶圓代工報價5%至15%,涵蓋各種制程,以爭取客戶投片,拉高產能利用率。

盡管半導體邁入庫存調節已超過一年,不少先修正的產品陸續有急單報到,但目前是傳統淡季、台積電、三星、聯電、力積電及世界先進等晶圓代工廠仍面臨淡季龐大重擔,首要之務是是撐起產能利用率,才能穩住財務表現,降價吸引客戶投片是最快、而且有效的手段。

業界人士分析,三星這波降價主要考慮要靠降價搶台積電先進制程客戶,同時也會對聯電、世界先進等形成壓力。

其實早在7nm階段,三星就曾靠“大大低於”台積電的報價爭取到英偉達,之後三星3nm GAA工藝的價格雖然也迎來了上漲,但是三星作爲追趕者,它的3nm價格還是比台積電便宜不少,因此三星的3nm趁機獲得了部分訂單。

除了更低的價格,另一個驅使芯片設計廠商選擇三星的原因,還在於台積電難以滿足所有客戶的訂單需求。因爲蘋果作爲台積電“財大氣粗”的大客戶自然獲得訂單優先權,畢竟台積電的先進制程產能也是有限的,承接蘋果之後,自然難以滿足所有客戶的訂單需求,彼時自然有一些訂單會流向可以穩定供貨的三星。

此外,三星還有一個隱形的利好,即芯片設計廠商絕不會希望芯片代工廠一家獨大,因爲倘若台積電獨家稱霸,必然會導致代工價格高企。

據BusinessKorea披露,三星目前在晶圓代工業務中,手機芯片的銷售收入佔54%,相關高性能計算(HPC)的AI服務器佔19%,自動駕駛芯片等汽車芯片業務佔11%。

預計到2028年,這個收入組合將會發生重大改變,目標是通過提高3nm及以下先進制程的完成度,確保獲得更多AI芯片客戶。三星計劃將手機領域的收入佔比降至30%以下,HPC的收入佔比提高至32%,汽車芯片的收入佔比提升到14%,外部客戶數量預計會比今年增加一倍。

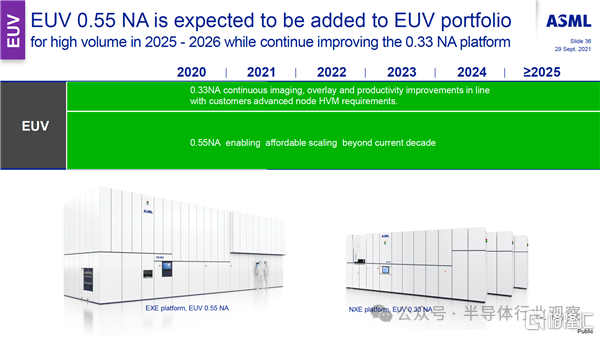

搶購EUV光刻機

對於晶圓廠商來說,決定先進制程量產的光刻機也有着同樣的地位。特別是在進入5nm、3nm,甚至2nm之後,EUV光刻機的數量將直接決定能否持續取得市場領先地位。

晶圓代工巨頭之間圍繞EUV光刻機的爭奪已經趨於白熱化。

據悉,三星將在五年內從ASML採購50套設備,每套單價約爲2000億韓元,總價值可達10萬億韓元。此外,ASML於去年12月中旬與三星籤署備忘錄,將共同投資1萬億韓元在韓國建立研究中心,並將利用下一代EUV光刻機研究先進半導體制程技術。

此前,三星電子宣布計劃到2025年擁有100台EUV光刻機。市場估計三星目前的EUV機群約爲40台。如果這50台設備的能夠順利交付,那么三星到2028年將能夠擁有約100台設備,這意味着三星將繼續提高產量,並在代工方面取得新進展。

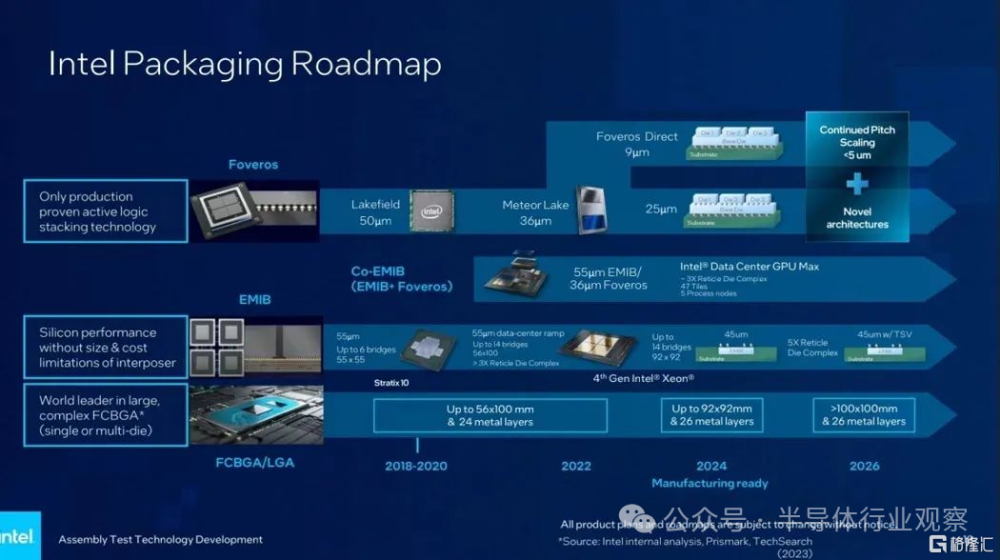

英特爾多路出擊

就在三星與台積電圍繞3nm先進制程激战正酣之際,沉寂已久的英特爾也在悄然卷入這場战局,在多個方面向台積電發起挑战。

IDM 2.0战略&轉型

2021年,英特爾新任CEO帕特·基辛格(Pat Gelsinger)在上任後不久,宣布了“IDM 2.0”战略,英特爾對外开放自己的代工服務,成立代工服務IFS業務,重返芯片代工行業。

在2022年9月舉行的英特爾技術創新峰會上,基辛格表示英特爾代工服務將开創“系統級代工的時代”,不同於僅向客戶供應晶圓的傳統代工模式,英特爾提供晶圓制造、封裝、軟件和芯粒。

晶圓制造:向客戶提供其制程技術,如RibbonFET晶體管和PowerVia供電技術等創新。

封裝:爲客戶提供先進封裝技術,如EMIB和Foveros。

芯粒:英特爾的封裝技術與通用芯粒高速互連开放規範(UCIe)將幫助來自不同供應商,或用不同制程技術生產的芯粒更好地協同工作。

軟件:英特爾的开源軟件工具,包括OpenVINO和oneAPI,加速了產品的交付,使客戶能夠在生產前測試解決方案。

這標志着從系統級芯片到系統級封裝的範式轉移,也是英特爾爲了更加开放自身代工服務的一個體現。

除了以“系統級代工”來加固自己的代工堡壘之外。英特爾還將自身芯片設計與制造進行解耦,讓英特爾實現更好的芯片設計和芯片制造能力,同時建立一個屬於自己的芯片代工生態。

四年五代技術節點,率先邁入2nm時代

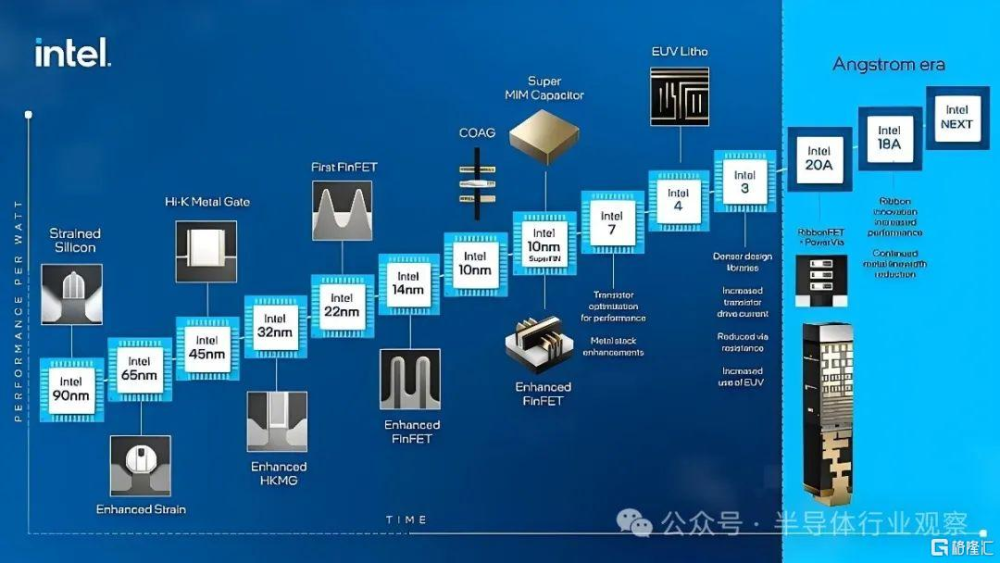

战略轉型之外,英特爾在流程路线圖方面也制定了一個雄心勃勃的目標,制定了“四年內實現五個技術節點”的快速小型化目標,將推進Intel 7、Intel 4、Intel 3、Intel 20A、Intel 18A五個流程節點,並計劃在2024年趕上並超越友商。

英特爾“四年五個制程節點”

(圖源:英特爾官網)

其中,Intel 20A是和台積電2nm對標的工藝,一旦英特爾成功突破Intel 20A量產,或有能力與台積電2nm一較高下。更先進的Intel 18A就是2nm以下的布局了。

英特爾的目標十分明確,試圖在芯片代工行業與台積電,三星形成三足鼎立格局,在高端芯片市場佔據一席之地。

2023年10月,英特爾宣布採用極紫外光刻(EUV)技術的Intel 4制程節點开始大規模量產。作爲英特爾首個採用EUV光刻技術的制程節點,Intel 4與先前的節點相比,在性能、能效和晶體管密度方面均實現了顯著提升。

目前,Intel 7和Intel 4已實現大規模量產;Intel 3正在按計劃推進,此前目標是計劃於2023年底量產。

採用Ribbon FET全環繞柵極(GAA)晶體管和PowerVia背面供電技術的Intel 20A和Intel 18A同樣進展順利,目標是2024年或2025年上市。英特爾將於不久後推出面向IFS客戶的Intel 18A制程設計套件(PDK)。

如果計劃順利,這將使英特爾成爲第一家成功轉向下一代工藝的芯片制造商,從而在全球半導體市場上佔據領先地位。

從核心技術的角度來看,英特爾的18A工藝無疑具有劃時代的意義。它將使得芯片的性能得到顯著提升,同時降低功耗和縮小芯片尺寸。這一技術的成功應用,將爲英特爾贏得更多高端芯片市場的份額,並進一步鞏固其在全球半導體行業的領導地位。

計劃通過Intel 18A工藝的推出和免費測試生產策略的實施,英特爾似乎正努力重振旗鼓,意圖重返半導體生產的領先地位。

值得一提的是,爲了吸引更多芯片設計公司的合作,英特爾甚至提供了免費測試生產的機會。這一策略不僅展示了英特爾對於自身技術的自信,也揭示了其希望通過廣泛合作來加速技術推廣和應用的市場策略。

通過提供免費測試生產機會,英特爾不僅降低了芯片設計公司的研發成本和風險,還爲其自身積累了寶貴的市場經驗和用戶反饋。這將有助於英特爾在未來的產品設計和生產中更加精准地把握市場需求和技術趨勢。

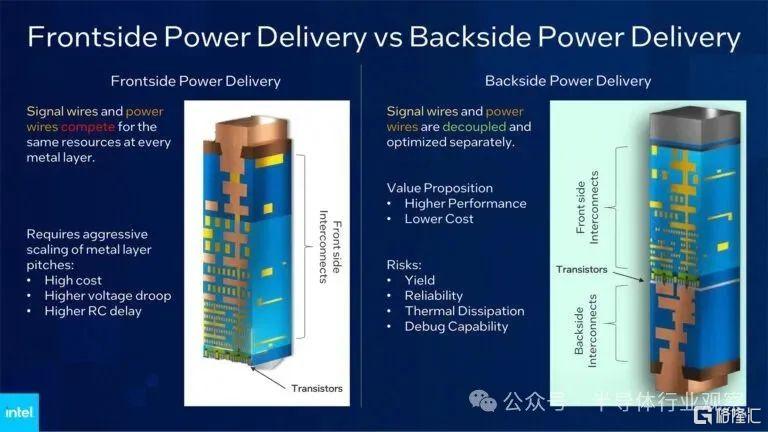

押寶背面供電技術

英特爾正在從傳統的FinFET工藝快速發展到基於全環繞柵極(GAA)晶體管和BSPDN(背面供電網絡)技術。

背面供電是一項頗具潛力的創新技術,可優化功率和時鐘的背面功率傳輸。英特爾成爲首家將其實踐應用的公司,據悉Intel 18A將採用BSPND技術,PowerVia是英特爾獨有的、業界首個背面電能傳輸網絡,通過消除晶圓正面供電布线需求來優化信號傳輸,通過將電力傳送到芯片背面而非正面,爲熱管理和整體性能提供了優勢。

有效的散熱和電力傳輸有助於優化芯片布局和設計,改進功能和熱量分布,這一創新的實施使英特爾再次站在半導體制造的最前沿。

基辛格指出,英特爾在背面供電技術方面提供了更好的面積效率。這意味着更低的成本、更好的動力輸出和更高的性能。他認爲Intel 18A略微領先於N2,因爲其晶體管更強大且功率傳輸能力更強。此外,與台積電相比,英特爾可以提供更有競爭力的價格優勢。

據了解,台積電和三星可能會在一兩年後跟隨英特爾進入背面供電領域。

拿下首台High-NA EUV光刻機

英特爾近日宣布,已經接收市場首套具有0.55數值孔徑(High-NA)的ASML極紫外(EUV)光刻機,預計在未來兩到三年內用於Intel 18A工藝技術之後的制程節點。

相較之下,台積電則採取更加謹慎的策略,業界預計台積電可能要到A1.4制程,或者是2030年之後才會採用High-NA EUV光刻機。

據了解,ASML將在2024年生產最多10台新一代High-NA EUV光刻機,其中英特爾就預定了多達6台。業界指出,至少在初期,High-NA EUV光刻機的成本高於Low-NA EUV,這也是台積電暫時選擇觀望的原因。台積電更傾向於採用成本更低的成熟技術,以確保產品成本和穩定性。

但需要注意的是,數值孔徑(NA)是光刻機光學系統的重要指標,直接決定了光刻的實際分辨率和最高能達到的工藝節點。ASML的高數值孔徑EUV光刻機,將NA值從0.33增加到0.55,更強的聚光能力意味着能夠處理更加精細的幾何尺寸,同時這也是繼續推進半導體制程進化的路线之一。

因此,英特爾作爲第一家使用高數值孔徑工具啓動大批量生產的公司,這將爲其帶來多項優勢。比如晶圓廠工具生態系統將不可避免地遵循其要求,上述要求可能會轉化爲行業標准,這可能會使英特爾比台積電和三星更具優勢。

據基辛格透露,英特爾最初就計劃利用新光刻機投產Intel 18A工藝,早在2022年1月,英特爾便搶先向ASML下定TWINSCAN EXE:5200,直接將下一代光刻機上市作爲“超車”的衝鋒號。但因爲時間上等不及,只能改用已有的0.33 NA NXE:3600D/3800E疊加雙重曝光。

因此,此次率先拿下0.55 NA EUV光刻機,領先對手幾季部署對英特爾而言是很大的優勢。

台積電的“守城”之道

作爲半導體行業的領導者,台積電在過去的30多年中立下了赫赫战功,成爲世界第一大芯片代工企業。

在面對三星和英特爾帶來的巨大挑战和壓力時,台積電需要審時度勢並採取有效的措施。

先進制程,台積電的“橋頭堡”

幾十年來,芯片制造商一直致力於制造更加緊湊的產品。芯片上的晶體管越小,能耗越低,速度也越高。

隨着芯片變得越來越小,從一代或“節點”工藝技術過渡到下一代工藝技術的挑战日益加劇,任何在下一代先進半導體領域佔據技術領先地位的公司都將處於主導地位。

在當前芯片代工領域,制程工藝依然是各大代工廠最大的核心競爭力。三星和英特爾都在加緊布局下一代制程工藝,希望從希望減少對台積電依賴的潛在客戶中受益,無論是出於商業原因還是地緣政治因素的考量。

不過,針對三星和英特爾的追擊,台積電董事長劉德音向業界表示“客戶還是看技術的質量”,透露出對台積電先進制程技術與良率優勢的信心。

隨着蘋果已經用上台積電3nm制程的芯片,更是幫助其進一步奠定了行業影響力。

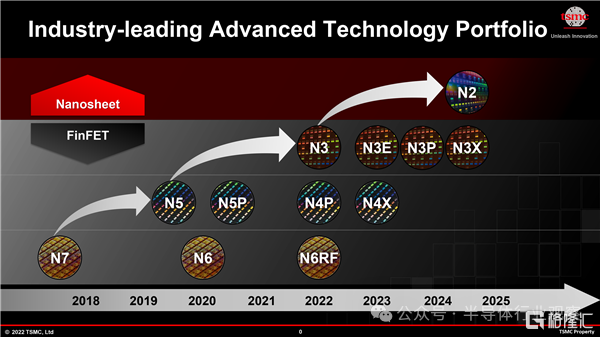

台積電目前規劃的3nm"家族"分別是N3、N3E、N3P、N3X、N3 AE,其中N3是基礎版;N3E是改進版,成本進一步優化;N3P性能將進一步提升,計劃2024年下半年投產;N3X聚焦高性能計算設備,計劃2025年進入量產階段;N3 AE專爲汽車領域設計,具備有更強的可靠性,將有助客戶縮短產品上市時間2~3年。

台積電工藝節點路线圖

據官方介紹:相較於N5制程技術,N3制程技術的邏輯密度將增加約70%,在相同功耗下頻率提升10-15%,或者相同頻率下功耗降低25-30%。台積電3nm工藝(N3)晶體管密度大約爲294.3MTr/mm2,遠要大於三星第二代3nm工藝的晶體管密度(三星第二代3nm工藝晶體管密度約爲194.6MTr/mm2)。

同時,對於英特爾率先計劃邁入2nm的雄心壯志,台積電總裁魏哲家似乎並不感到擔憂。他在去年10月份的內部評估中指出,台積電最新的3nm工藝(已上市)在功率、性能和密度方面可與Intel 18A相媲美。這意味着,至少在技術層面,台積電並未落後於英特爾。

台積電總裁魏哲家表示,根據內部評估,N3P工藝在性能與能效上與Intel 18A技術相當,但上市時間更早,技術上也更爲成熟,而且成本還要低得多。同時還重申台積電的N2工藝(2nm)優於競爭對手的Intel 18A,推出時將成爲半導體行業最先進的技術。

據悉,台積電計劃在2nm制程節點採用GAAFET晶體管,同時將會在2026年發布的N2P工藝引進Nanosheet GAA晶體管並添加背面電源軌技術,制造的過程仍依賴於現有的EUV光刻技術。台積電認爲引入新一代技術後,N2工藝將在功率、性能、面積上全面勝出。

據知情人士透露,前不久台積電已經向蘋果和英偉達等一些最大客戶展示了其“N2”原型的工藝測試結果。

毋庸置疑的是,台積電在先進制程的步伐確實要更快且更穩,但憑借多年來積累的豐富經驗和豐厚訂單,無疑爲其提供了巨大的底氣保障和客戶基礎,因此想要在先進制程領域挑战台積電絕非易事。

綜合來看,在這場先進制程的競賽中,台積電、三星和英特爾都在積極投入研發,力圖率先實現技術突破。台積電憑借其豐富的技術積累和強大的研發能力,在2nm技術的研發上展現出了強大的實力;三星則通過率先採用GAA晶體管架構,在技術領先時間和架構過渡方面贏得了優勢;而英特爾則通過推出Intel 18A工藝節點,展示了其在半導體技術領域的創新能力。這三家公司的技術競賽無疑將推動2nm制程技術的快速發展。

圖源:TRENDFORCE

除了技術創新外,市場策略也是決定競爭勝負的關鍵因素。台積電通過向蘋果等大客戶展示2nm原型芯片,穩定了其高端市場份額;而三星則採取低價策略,吸引包括英偉達在內的大牌客戶,意圖擴大市場份額;英特爾則通過提供免費測試生產機會,與芯片設計公司建立廣泛的合作關系,共同推動2nm技術的發展。這三家公司的市場策略各具特色,將在未來形成激烈的市場競爭。

有分析師認爲,台積電在成本、效率和信任方面仍然具有優勢,將保持其在該領域的全球霸主地位,但三星電子和英特爾已將即將到來的2nm技術視爲縮小與台積電差距的重要機會。

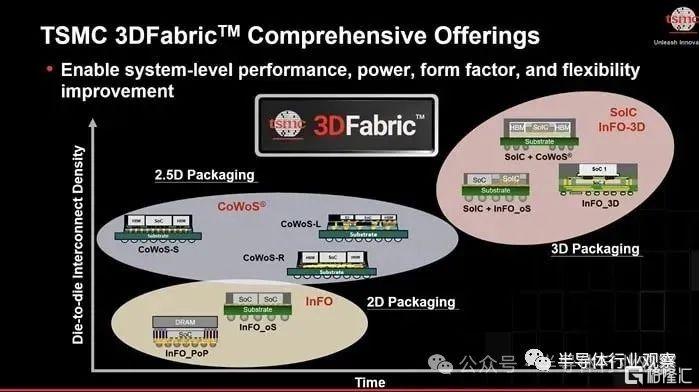

先進封裝,台積電的另一把尖刀

在摩爾定律逐漸放緩的趨勢下,僅僅從微縮晶體管,提高密度以提升芯片性能的角度正在失效。對此,先進封裝成爲後摩爾時代彌補芯片性能和成本的重要解決方案之一。

先進封裝技術趨勢在於提高I/O數量及傳輸速率,以實現芯片間的高速互聯。爲了適配高性能運算、AI、5G等應用的最新需求,封裝形態從2D邁向2.5D、3D的進程不可避免。

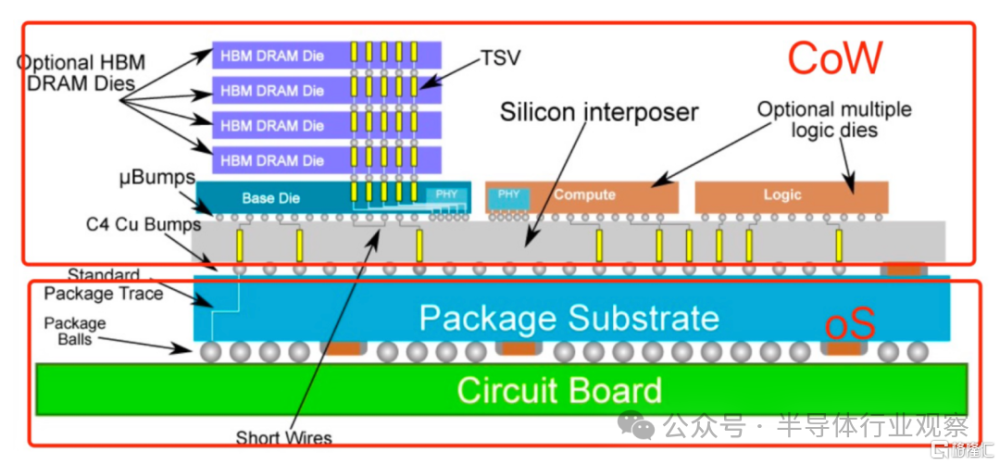

市場格局中,台積電是全球先進封裝技術的領軍者,旗下3D Fabric擁有CoWoS、InFO、SoIC等多種先進封裝工藝。

其中,CoWoS是台積電最經典的先進封裝技術之一。2011年至今,台積電的CoWoS工藝已經迭代至第五代,期間中介層面積、晶體管數量、內存容量不斷擴大。英偉達、AMD、博通、Marvell等都是台積電CoWoS工藝的大客戶。

台積電CoWoS結構示意圖

自去年AIGC的爆火之後,CoWoS也隨之成爲行業焦點。據悉,繼英偉達2023年10月確定擴大下單後,蘋果、AMD、博通、Marvell等重量級客戶近期也對台積電追加CoWoS訂單。

爲應對大客戶需求,台積電加快CoWoS先進封裝產能擴充腳步。援引台積電消息,預計2023年CoWoS產能將較2022年實現倍增,2024年CoWoS產能將在2023年基礎上再次實現倍增。2022年台積電CoWoS營業收入已經佔總營業收入5%以上,並且將以20%的年增速保持增長,高於台積電預估的總營業收入年增速10%。

此外,台積電還开發了廉價版的CoWoS技術,即InFO技術,降低了單位成本和封裝高度。這也是InFO技術在移動應用和HPC市場成功的重要原因,爲台積電後來能獨佔蘋果A系列處理器打下了關鍵基礎。

除了CoWoS和InFO,2018年,台積電首度對外界公布了創新的系統整合單芯片(SoIC)多芯片3D堆疊技術SoIC。SoIC是基於台積電的CoWoS與多晶圓堆疊(WoW)封裝技術开發的新一代創新封裝技術,這標志着台積電已具備直接爲客戶生產3D IC的能力。作爲業內第一個高密度3D chiplet堆疊技術,SoIC被看作“3D封裝最前沿”技術。

相較2.5D封裝方案,SoIC的凸塊密度更高,傳輸速度更快,功耗更低,或將成爲行業未來發展的主要封裝技術趨勢。

當前,台積電也正在積極上調SoIC的產能計劃,計劃到2024年年底,月產能躍升至5000-6000顆,以應對未來AI和HPC的強勁需求。當前,AMD和蘋果對台積電的SoIC產品非常感興趣,前者是台積電SoIC的首發客戶,後者計劃讓SoIC芯片搭配熱塑碳纖板復合成型技術,擬應用在Mac、iPad等產品上。

可見,台積電憑借其領先的先進封裝技術喫盡紅利。當然,英特爾,三星兩位強敵也絲毫不懈怠。

英特爾通過多年技術探索,相繼推出了EMIB、Foveros和Co-EMIB等多種先進封裝技術,在互連密度、功率效率和可擴展性三個方面持續精進。在今年5月,英特爾發布了先進封裝技術藍圖,計劃將傳統基板轉爲更爲先進的玻璃材質基板,以實現新的超越;而且,英特爾也在布局硅光模塊中的CPO(共封裝光學)技術,通過玻璃材質基板設計,利用光學傳輸的方式增加信號交換時的可用頻寬,以優化算力成本。

英特爾先進封裝路线圖

(圖源:英特爾官網)

2023年英特爾擴增了其位於馬來西亞的先進封裝產能,目標是在2025年將先進封裝的產能較當前提升4倍。

結合此前英特爾在先進制程上一系列動態,外界預期,英特爾將結合先進制程與先進封裝兩條线,希冀在晶圓代工領域實現“1加1大於2”的效果。

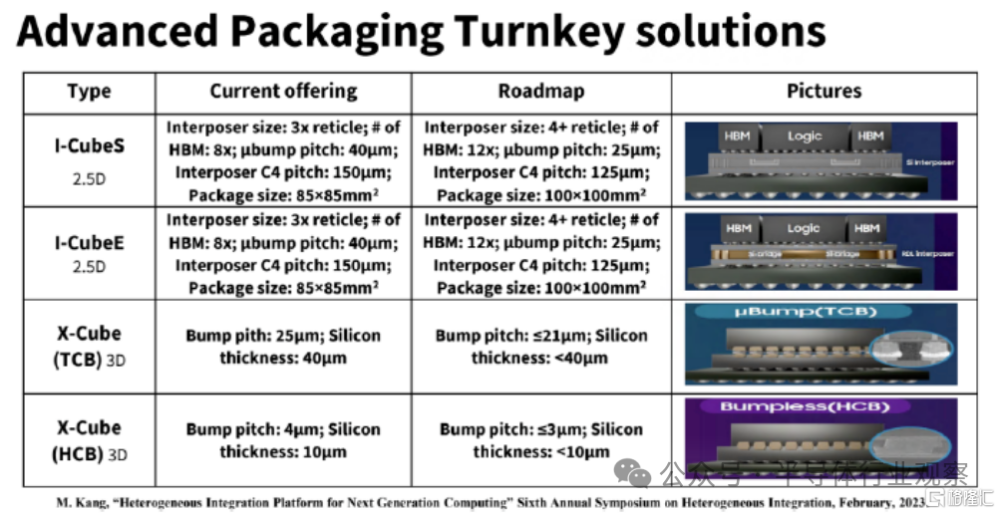

三星在2.5D/3D先進封裝技術領域也有布局,並已經推出I-Cube、X-Cube等先進封裝技術。針對2.5D封裝,三星推出的I-Cube技術可以和台積電的CoWoS技術相媲美。針對3D封裝,三星在2020年推出X-Cube技術,將硅晶圓或芯片物理堆疊,並通過硅通孔(TSV)連接,最大程度上縮短了互聯長度,在降低功耗的同時提高傳輸速率。

另外,三星計劃在2024年量產可處理比普通凸塊更多數據的X-Cube封裝技術,並預計2026年推出比X-Cube處理更多數據的無凸塊型封裝技術。擁有從存儲器、處理器芯片的設計、制造到先進封裝業務組合的優勢。

三星先進封裝技術路线圖

(圖源:方正證券研究所)

2nm是工藝的決战,也是先進封裝的交鋒。先進封裝與制程工藝可謂相輔相成,在提高芯片集成度、加強互聯、性能優化的過程中扮演了重要角色,是性能持續提升的重要保障。對於在工藝節點時間上的爭奪,先進封裝已成爲三大巨頭“不可忽視”變數。

但事實上,由於台積電CoWoS先進封裝技術的領先性,英特爾和三星在當前的先進封裝之爭中並不佔優勢,爲了爭奪未來先進封裝市場份額,正在开發更先進的封裝技術展开競爭。

更多先進封裝詳細技術細節和廠商布局情況,筆者在前文中有過詳細介紹,感興趣的朋友可以跳轉了解,在此不過多贅述。

客戶優勢顯著

芯片領域的競爭不僅是技術上的挑战,也是商業上的博弈。各大芯片制造商都在尋求與客戶建立長期的合作關系,以確保其未來的收入和利潤。

這也是台積電多年來高枕無憂的關鍵所在。

據了解,台積電爲幾乎全世界主要芯片开發商制造芯片,包括蘋果、高通、英偉達、AMD、聯發科、賽靈思、索尼等,緊密地客戶關系給台積電提供了強大的抵御外來風險能力。

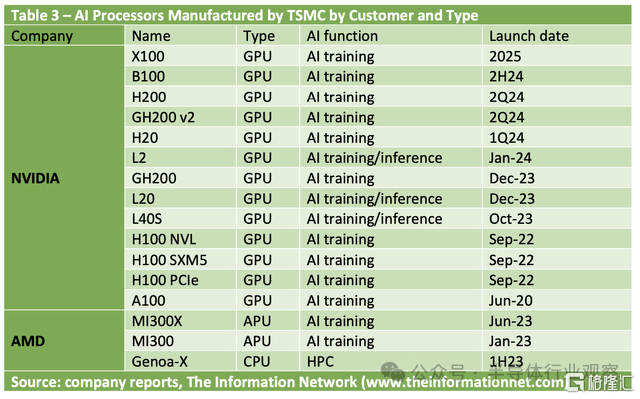

在目前由英偉達和AMD主導的AI訓練和推理領域最重要的AI處理器市場中,台積電更是生產了這兩家公司的整個芯片組合。

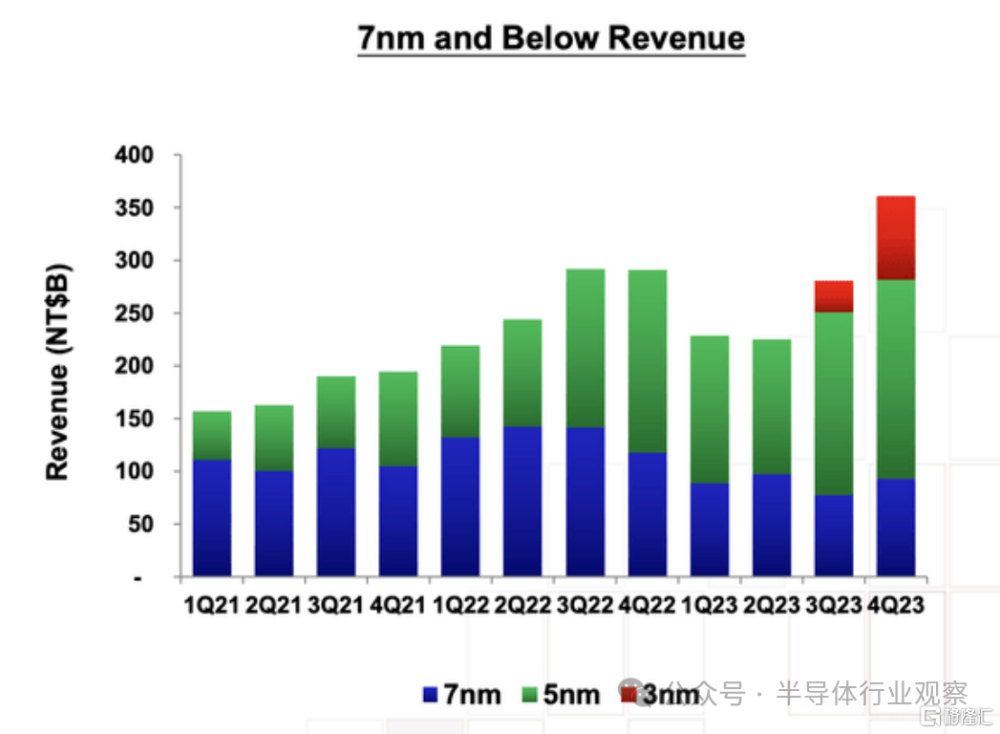

從技術分類來看,先進制程工藝對台積電業績貢獻較爲明顯。台積電3nm制程工藝在2023年第四季度佔晶圓總收入的15%,5nm和7nm分別佔35%和17%;先進制程(7nm及以下)佔晶圓總收入的67%。

根據其2023年Q4財務報告顯示,台積電3nm芯片銷售額達到總銷售額的15%,7nm及以下技術的銷售額佔比高達67%。

其中,5nm是台積電最大營收的制程工藝,這一制程工藝在量產初期的主要客戶是蘋果,隨後又有更多的客戶轉入,包括AMD、高通、聯發科、英偉達、賽靈思等,衆多大客戶的爭搶導致台積電5nm連連爆單。隨後隨着ChatGPT的爆火,帶動AI芯片和服務器處理器芯片、HPC領域客戶投片量增加,5nm需求再次直线拉升。台積電的7nm技術不僅適用於PC、平板電腦和智能手機,還適用於數據中心、汽車以及爲人工智能執行復雜的訓練和推理。

Counterpoint Research指出,憑借蘋果的推動,3nm制程工藝在整體晶圓收入中佔比6%,隨着高通、聯發科和更多高性能計算客戶在2024年採用3nm制程,預計將有進一步增長。

另一方面,台積電的良率優勢,也是其在先進制程上獲得客戶青睞的關鍵原因。

衆所周知,良率是檢驗新工藝是否真正量產以及具備競爭力的關鍵,良率一旦不達標,制造成本大增,沒有商業可行性。

在實際應用中,由於台積電穩定的良率也使其收獲了多筆從三星等其他代工廠轉來的訂單。比如在10nm和7nm制程剛剛量產的時候,高通和英偉達就分別把驍龍855、865和7nm制程GPU芯片轉移到了台積電,隨後在4nm制程興起時,高通又將驍龍8Gen1Plus的生產訂單轉給了台積電。

據台積電此前透露,3nm工藝的良率跟5nm工藝初期量產時的良率相當,台積電跟客戶聯合研發新品,並开始大量生產。從台積電的表態來看,雖然沒有具體公布良率多少,但是他們的3nm良率顯然比較靠譜,至少客戶是同意开始生產的,意味着商業上是劃算的。

然而,盡管台積電在技術和良率上擁有領先優勢,一些跡象顯示,客戶們仍然有意考慮選擇其競爭者,客戶也在尋求多元化的供應商,以降低對單一芯片制造商的依賴。

一位行業資深分析師表示,出於效率和競爭需要,台積電仍然會是業內頂尖公司的第一選擇,但是,對於激烈競爭中的公司們來說,需要其他代工廠來分散風險。

但英特爾和三星的業務結構引起了許多潛在客戶對可能的技術或設計泄露的擔憂,因爲三星和英特爾既要爲自己生產芯片,又要尋求爲其他芯片領域的競爭對手如高通、AMD和英偉達提供芯片代工服務,存在直接競爭的關系。

盡管三星和英特爾拆分了代工業務,強調保護客戶敏感設計數據,但客戶選擇其代工難免會有技術或設計泄露的擔心。

台積電無寶不落,但變數仍在

綜合三巨頭布局策略和方式來看,尤其是在三星和英特爾率先發力下一代先進制程的情況下,台積電被廣泛認爲是一個保守技術开發者,其傾向於確保新技術的成熟和可靠性,然後再進行部署,而不是急於將新技術推向市場。

從實際的市場表現來看,台積電此舉可以降低技術失敗的風險,提高其芯片的產量和質量,從而確保客戶的滿意度。

例如,三星在2018年开始在其7nm工藝中使用EUV光刻機,然而台積電選擇等待。直到EUV工具的穩定性和成熟性得到確認,以及相關問題得到解決或至少得到確定,才在2019年的N7+工藝中开始使用EUV。

此後,在FinFET向GAA工藝的過渡上,台積電依舊重操這一模式。憑借工藝領先性和生產良率上的技術優勢和積累完全有實力與採用GAA技術架構的三星抗衡。

在英特爾大力押注的BSPDN背面供電技術上,台積電依舊不緊不慢,計劃將在2026年底才开始大規模生產的N2P上加入。

這種謹慎的方法有助於台積電確保其制程技術的穩定性和可預測性,從而提供高質量的芯片給其客戶。

但從先進封裝領域來看,台積電則一改常態,積極布局率先落地,在先進制程與先進封裝的組合拳下,爲其帶來了新的增長浪潮。

在這張弛有度的策略下,充分凸顯着台積電的战略哲學和獨到眼光。在其看准的藍海賽道,台積電始終敢爲人先,無論是十年前率先試產16nm FinFET制程技術超越英特爾,還是五年前部署先進封裝收獲如今的AI紅利,台積電都精彩演繹了所謂鳳凰無寶不落。

而在其保持較大優勢的先進制程領域,縱然面對三星和英特爾的步步緊逼,台積電沒有選擇盲目激進,反而採取了先觀察再跟隨的策略,在做好充分的准備和規劃後“亦步亦趨”,憑借自身強大的產能、良率和客戶基礎的基本盤優勢,維持不敗之地。

“英特爾曾經是保守派”,如今情況似乎發生了轉變。

古人有雲“打江山易,守江山難”,台積電並沒有成爲代工市場絕對的贏家。

台積電一家的產能,縱然難以維持龐大的先進制程市場。哪怕三星和英特爾的芯片會陷入性能或良率“滑鐵盧”的風險,也依舊會有大批廠商在產能和價格因素的驅動下,愿意去“嘗嘗螃蟹”。

未來,圍繞先進工藝芯片之爭將在台積電、三星和英特爾之間展开,代工三巨頭的拉鋸战也將成爲推動摩爾定力繼續前行的動力,推動下一個“彎道”的到來。

每一個車手都明白彎道代表着太多可能,當一個時代开始轉彎,領先者可能會落後,落後者可能會超越。

標題:台積電“攻防战”

地址:https://www.iknowplus.com/post/79528.html