芯片技術的挑战者“大閱兵”

自1971年英特爾推出第一款4004芯片以來,集成電路中的晶體管數量以驚人的速度增長。現在,半導體行業不得不承認,“微芯片上的晶體管數量大約每18個月增加一倍”通過調整晶體管大小來跟上摩爾曲线的心血管是不可持續的,維持這種進步速度的成本是天文數字——晶體管密度每增加一倍,就需要資本投入同時增加一倍,而且物理問題也層出不窮。

但人工智能、5G和數據中心等應用對芯片的需求仍在繼續,半導體仍要繼續發展。行業也並沒有放棄摩爾定律,只是每一次的進步都異常艱難。在芯片繼續演進的前路,各技術齊上陣,展示着各自的實力和潛力,但也各有各自的限制和不足。

封裝技術

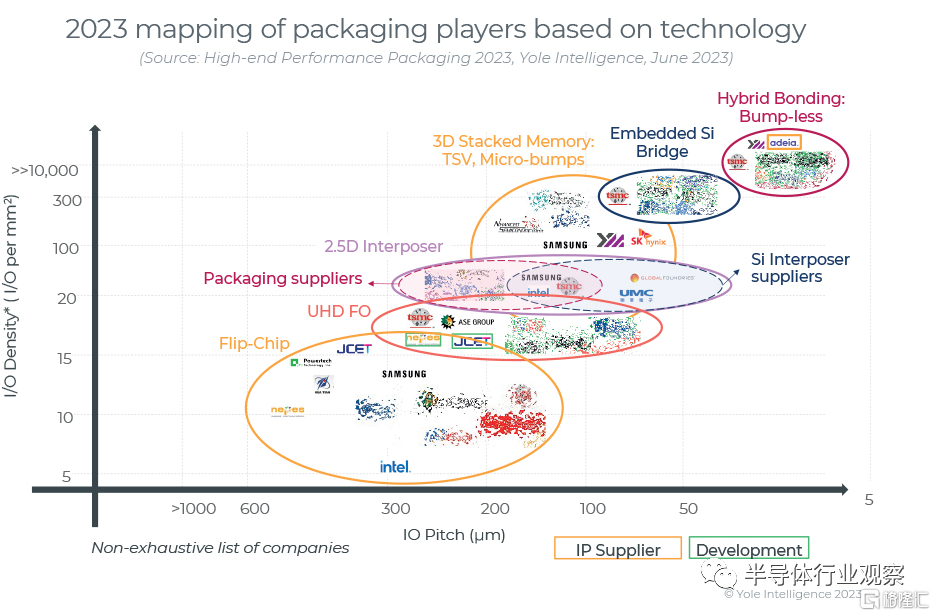

首先是封裝技術。封裝技術是一項無法進行的功率計算。隨着大功率需求的提升,以及單芯片向更先進的制程推進引腳的增加,芯片性能的進步更多地依賴於包括重要封裝、曾經,封裝方案被認爲是承載和連接半導體所必需的組件。現在,先進封裝被認爲是推進半導體技術先進性前沿的機會,封裝的一大優勢就是它可以相互增加連的密度,從而提高信號速度和整體處理能力。這促使企業大力投資先進封裝研究和資本。也因此,《先進封裝,轟動大爆發》,據Yole預測,封裝市場在2022年的價值22億美元,預計到2028年將超過160億美元,2022-2028年的復合年將爲40%。

先進封裝玩家一覽

(圖源:Yole)

頂尖的先進封裝技術都掌握價值在晶圓代工封裝上,由於先進封裝提供了比傳統封裝封裝更高的機會,因此主要參與者和快速追隨者正在开發各種形式的封裝技術其商業化,以此贏得優質客戶。台積電、英特爾和三星是推動先進封裝創新的主要參與者。台積電利用CoWoS、InFO和3D SoIC解決方案提供了3DFabric技術平台。英特爾也積極布局2.5D/3D封裝技術,如Foveros、 EMIB和Co-EMIB產品,以及繼承的Foveros Direct & Omni。三星有I- CubeS 、H-Cube,以及繼承的R-Cube和X-Cube等2.5D和3D封裝技術。因此它們之間,都圍繞着先進性封裝的競爭也愈加疲勞,《代工黨“拼”先進封裝》。

從硅技術上來看,他們主要採用了採用Through-Silicon Via,TSV)、模具通孔(Through-Mold Via,TMV)、微凸塊和混合鍵合等技術來縮小互連長度。3D封裝發展的初期主要是通過裸片上的一個小銅凸塊來提供芯片之間的垂直連通。凸塊的尺寸範圍只能從40 µm到最終縮小到20 µm或10 µm尺寸,混合鍵合技術是實現10μm及以下間距另一個有潛力的連接技術,它利用小型的銅對銅連接來連接封裝中的裸片,能夠爲3D封裝提供卓越的互聯密度。

除此之外,晶圓代工廠商甚至开始向封裝材料上進,英特爾於9月18日,對外披露了其半導體玻璃關鍵技術的开發進展,《开啓了下一代封裝革命》。英特爾認爲,有機材料不僅消耗更多的電流,且具有膨脹和翹曲等限制,到2030年前,半導體產業很可能會達到使用有機材料在硅封裝上延展電晶體數量的極限,玻璃基板將是下一代半導體確實可行且堆積器的進展。 搭建主機基板,玻璃基板具備卓越的機械、物理和光學特性,在單一封裝中可連接更多電晶體,提高延展性並能構成更大的系統級封裝(SiP)芯片架構師將能夠在一個封裝上提供更小的封裝、更小的芯片,同時獲得更高的彈性、更高的總體成本和功耗,實現同樣的效果並增加密度。

互聯技術

“互連”也是芯片技術挑战的重要參與者。曾經,晶體管的速度是抵消芯片性能的限制因素,但隨着當今動極數百萬晶體管芯片的出現,更多的晶體管使得线路的電阻也承受另外,在間隔非常近的互連线路之間可能會發生電容耦合。這兩者都影響了信號的傳輸。其次,芯片的計算能力(FLOP)在每一代芯片/封裝中增長速度均快輸入和輸出數據的速度。如今,互連已經成爲一大限制。

在芯片互聯技術上,目前銅互連仍然是普遍普遍的做法。1997年,IBM率先從鋁互連轉向銅互連,自那時起,銅互連一直是用於制造邏輯放大器(BEOL)應用但隨着芯片工藝邁入更先進的工藝,在10nm尺寸越來越小,銅的電阻率將會增加,從而开始影響電子電路的性能。

於是,行業也隨之發起對銅以外的新材料的探尋。研究顯示,鈷(Co)、釕(Ru)、釕(Rh)、銥(Ir)和鉬(Mo)等材料在尺寸更小下具有更好的抵抗表現。除此之外,像imec這樣的研究機構在大約五年前就开始爲未來互聯應用尋找替代二元和三元合金金屬的研究。具體可查看《替代銅互連,新的裏程碑一文。但是想要新材料替代銅互連,並非易事。《銅互連,還是無法替代?》

互聯不僅包括硬件層面的物理互聯,還包括更高層次的接口和協議技術(如不同設備或系統之間的通信接口和標准)。如PCIe、以太網、NVMe、Linux、TCP/IP、RDMA這些接口技術都在互聯方面發揮着重要的作用。近些年來,在數據中心存儲和數據處理的爆炸性需求,以及傳統的DDR內存接口的帶寬和容量擴展有限的情況下,一些新型的接口互聯技術被开發出來。

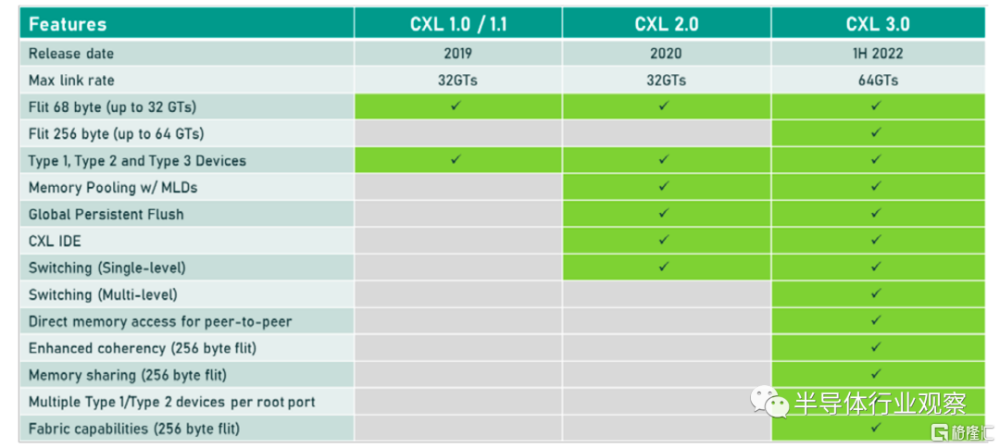

其中一個互聯技術的挑战者是,英特爾於2019年3月在InterconnectDay 2019上推出开放性互聯協議Compute Express Link (CXL),已成爲業界和學術界認爲最有前景的接口技術之一,因爲它不僅可用於內存容量和帶寬的擴展,還能夠實現內存的拆分。這幾年其標准發展迅速,知名芯片廠商已在其產品布局中宣布支持CXL。在《揭开CXL內存的神祕面紗》一中對CXL進行了精彩的描述。

不同版本CXL對比

(來源:CXL3.0PDF)

另外一個就是現在大火的Chiplet,在後摩爾時代,Chiplet這樣的先進封裝技術在推動芯片性能繼續提升上關鍵。其接口技術標准UCIe也於2022年推出,發展至今,UCIe聯盟已經發布了兩個一個版本,分別是UCIe 1.0和1.1。《Chiplet,怎么連?》一文中指出,Chiplet當前正處於一個發展階段,能否成爲一種新的IP產品和商業模式,甚至拯救摩爾定律的救星,關鍵就在於目前尚未達成統一的Chiplet互聯標准,建立一個开放和標准化的Chiplet生態。

另外,還有一些公司推出強調的互聯技術,例如英偉達的NVlink技術,它在今年早些時候推出了一款獨立的128端口NVLink交換機系統,配備800G OSFP接口,可直接連接多達256個Hopper H100 GPU。

硅光芯片也是一項有潛力的技術,隨着近年來光子芯片的廠商越來越多,例如Intel、Ayar Labs、博通、思科、國內還有曦智科技等一家頭部企業。提升光電傳輸的速度,有效解決目前元件使用銅導线所面臨的信號耗損機熱量隨之而來的問題,,被寄予厚望的《光芯片照明計算機黃金時代》。但硅光子仍面臨着高制造成本、光源集成、材料匹配、熱效應等瓶頸。

據650集團研究機構發布的《數據中心互連半導體預測與研究報告》中指出,數據中心計算現在和未來幾年的發展代表着架構的轉型。互連芯片的創新和技術轉型將大幅提高每個單位功率和每單位成本的系統I/O帶寬,從而實現人工智能和加速計算集群的尺寸和代際的擴展。數據中心互連半導體市場(即支持跨計算、存儲和網絡系統的高性能數據通信)芯片技術的價值)預計將在2022年至2027年內翻一番,達到近250億美元,年復合達到這幾個數字。

新的供電方式

隨着我們不斷縮小晶體管和IC的尺寸,供電成爲片上的一個重大挑战。根據應用材料的介紹,目前所有芯片都需要從芯片的前端提供電力,這大約需要通過超過12層的布线,引腳晶體管。方法有兩個主要限制:芯片上寶貴的空間必須分配給電源线,而且當電源突破到達閾值時會損壞電源。背面供電(BPDN)或有助於挽救摩爾定律。

背面供電網絡的基本思想是去掉所有從硅表面上方發送電力(而不是數據信號)的互連,把它們放置在硅表面下方。理論上這可以減少功率損耗,因爲功率傳輸互連可以更大且電阻更小。它還爲信號承載互連釋放了晶體管層上方的空間,可能導致更簡潔的設計。

目前包括imec、英特爾(PowerVia)、台積電、三星等都在研發這項技術,一些芯片制造商已公开宣布在2nm及以上技術節點的邏輯IC中引入背面供電網絡。 《背面供電技術,越來越多》熱!》背面但是供電技術需要的器件架構、新材料开發、材料的單片和獨立集成、更大的晶圓尺寸和單晶圓處理,才能滿足此前的應用要求。

新型材料

新型材料也是焦點之一。過去幾十年,硅材料是芯片行業的統治者。根據赫爾辛基大學設備研究與工程實驗室教授 Deep Jariwala 的說法,“我們已經達到了這樣一個進步,即使你可以繼續縮小硅,它已經到了不再節能的地步。”因此,行業研究學者對新型材料的探索孜孜不倦。潛在的硅替代者主要有二維材料如石墨烯、各種氧化物、金剛石、有機材料等。被視爲未來芯片技術的希望。

包括台積電和英特爾的商業企業,以及麻省理工、赫爾大學等科研機構已經對二維材料進行了不同程度的研究,其中,大量的研究報告表明,基於二維過渡金屬二硫族化合物如MoS2和WSe2的晶體管是接替硅的重要候選者。《工會开始,七篇論文,二維材料的新進展》。隨着行業對二維材料研究的增加,其已逐步走向制造。

碳納米管(CNT)是另一種被寄予厚望的新材料,被認爲是下一代高性能、超大規模和晶體管晶體管以及光電器件的候選者。碳和硅一樣,不是什么新材料,來自碳納米管管子可能被安裝在高性能數字電子設備以及射頻和傳感應用的平台上。而且它可以通過化學氣相沉積(CVD)方法,能夠在CMOS工廠成功制造。《下一代的晶體管替代,不是硅!》一篇文章對碳納米管進行了詳細的介紹。

二氧化鉿這樣的新型材料爲存儲其實新型存儲提供了更多的可能性。通過研究發現,二氧化鉿具有鐵電的特性,這樣的好處是它在不供電的情況下也可以長久存儲數據,意味着其價值可以再非易失性內存領域發揮。總而言之,《鉿基氧化物材料有望成爲未來芯片的選擇》。

結語

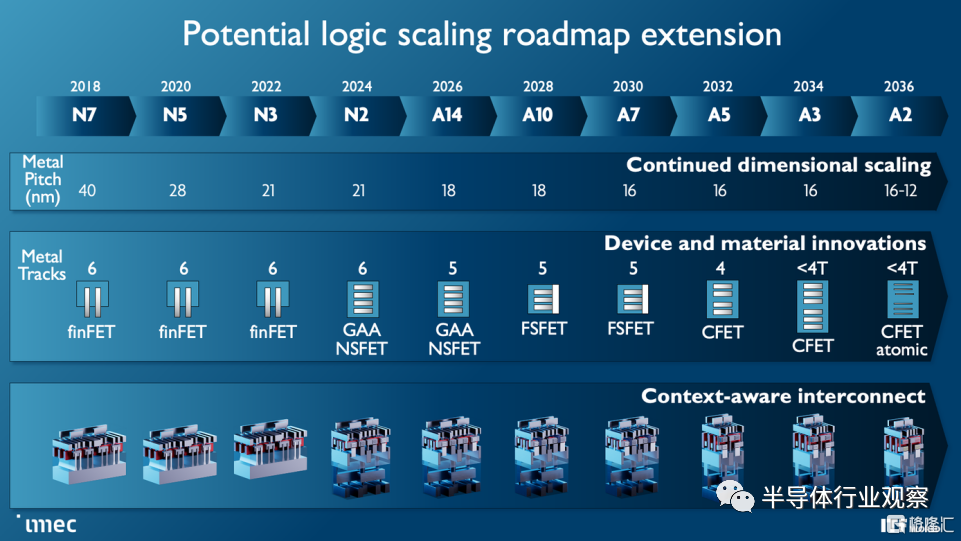

Imec 預測,晶體管的形式將在未來十年發生變化,連接它們的金屬物種會發生變化。最終,晶體管可能是由二維半導體而不是硅片制成的器件,電力傳輸和其他基礎設施可以分層放置在晶體管底部。爲了保持摩爾定律的正常運行,所有可能的槓杆都會被拉動,除了前面提到的這些,還有下一代光刻技術、工具等各領域的支持。最終,我們可以將摩爾曲线延伸到什么程度可能完全是一個經濟學問題。

Imec的CMOS 2.0路线圖,很有趣

標題:芯片技術的挑战者“大閱兵”

地址:https://www.iknowplus.com/post/38100.html