向下一代晶體管邁進

由於需要在同一基底面內垂直分離 nMOS 和 pMOS 器件,因此开發能夠展示單片互補場效應晶體管 (CFET:complementary FET) 晶體管結構功能的工藝流程非常復雜。在這篇文章中,來自 imec CFET 團隊的三位專家 Hans Mertens、Steven Demuynck 和 Anne Vandooren 解釋了他們是如何逐步解決這種復雜性的。他們重點介紹了 CFET 特有的工藝步驟和模塊,並將背面連接作爲進一步縮小標准cell尺寸的關鍵技術。

imec 首席技術人員Hans Mertens首先指出,如今,半導體行業正處於從 FinFET 向納米片(Nanosheet)過渡的時期。在這一過程中,我們可能會引入 Forksheet,這是我們幾年前提出的一種先進的納米片架構,它減少了相鄰器件之間的間距,與傳統納米片相比,具有擴展性和性能優勢。

“到本世紀末,我們預計互補式場效應晶體管(CFET)將會出現。在這種器件結構中,n-和 pMOS 器件相互堆疊,首次從標准單元高度的考慮因素中消除了 n-p 分離。如果輔以先進的晶體管接觸技術,CFET 將能把軌道高度(track heights)從 5T 逐步提高到 4T 甚至更高,從而有效地大幅縮小標准單元尺寸。”Hans Mertens說。

從加工角度來看,由於 nMOS-pMOS 垂直堆疊結構,CFET 的制造具有挑战性,而我們正處於探索的早期階段。目前已經提出了幾種 CFET,包括單片和順序工藝流程(monolithic and sequential process flows)。在順序工藝流程(sequential process flow)中,頂層器件在底層器件上通過晶圓鍵合轉上空白半導體層後,按順序進行加工。而單片集成則是在單一基板上構建垂直器件架構。"

單片 CFET:引入 CFET 的最快途徑

imec 首席技術人員 Anne Vandooren則強調,在其邏輯計劃中,imec 及其合作夥伴重點關注單片 CFET 集成,因爲與現有的納米片型工藝流程相比,這種集成方案的破壞性最小。因此,它被認爲是以工業相關尺寸推出 CFET 的最快途徑。

不過他也重申,盡管如此,垂直堆疊層(這兩種器件都將由垂直堆疊層制造)仍需要高縱橫比圖案化、材料的選擇性沉積和去除,以及高質量(外延)薄膜的沉積。此外,還需要引入一些 CFET 專用工藝模塊,以便在橫截面的柵極和接觸部分實現垂直隔離。

爲了應對這些挑战,imec將單片 CFET 集成挑战劃分爲不同的子項目,並逐步提高集成復雜度。每個子項目都基於不同的測試工具。我們首先關注的是單極單片 CFET,其 n 和 p 上下器件在不同的晶圓上加工。其他測試工具將採用在同一晶圓上加工的單片式 CMOS CFET 器件。兩者的主要區別在於 CFET 器件的接觸方式,最終將實現先進的中間线 (MOL) 和背面連接選項。

“對於每種不同的測試,我們都會探索各種工藝和集成方案,在功率-性能-面積收益與復雜性之間進行權衡。” Anne Vandooren接着說。

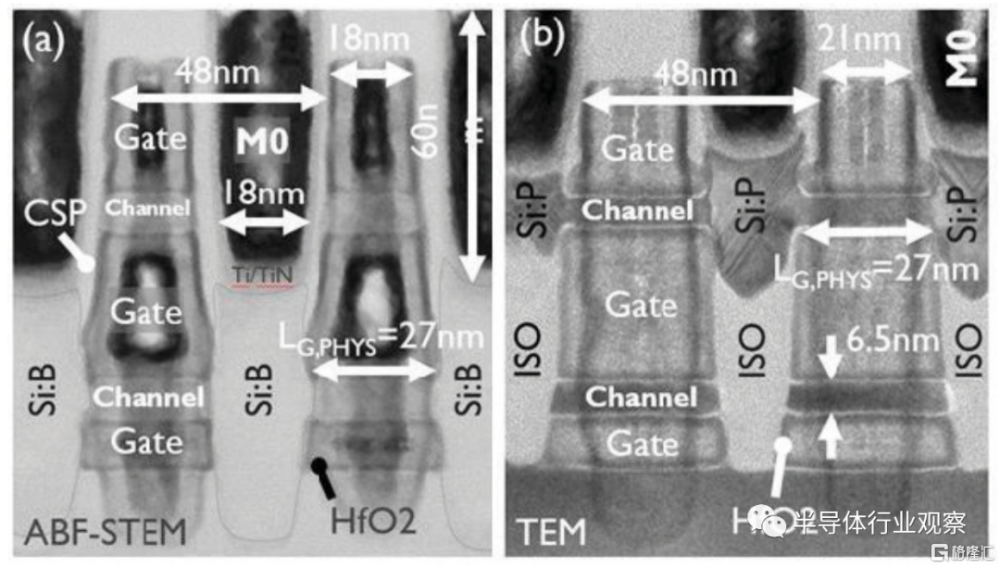

48 納米柵間距單極單片 CFET 演示

從Hans Mertens的介紹我們得知,在 2023 年 VLSI 技術研討會上,imec 展示了通過單片集成技術制造的單極性 CFET 器件,其柵間距爲 48nm [1]。這項工作(圖 1)被選入 2023 年 VLSI 技術研討會亮點環節。我們的功能器件在 n- 和 pMOS 下分別顯示出底部和頂部器件的出色开關特性。我們目前正在探索以更小的柵極間距集成單極單片 CFET。

在這次演示中,對底部或頂部器件的源漏外延結構(源漏外延)和源漏接觸進行了評估。此外,爲了限制長寬比並加快开發速度,結構的有源部分在底部器件和頂部器件中分別只有一個納米片。然而,這項工作的意義在於表明,在頂部和底部薄片之間的垂直間隔僅爲 30 納米的情況下,我們找到了一種能使頂部和底部器件獨立接觸的方法。它是按比例尺寸實現先進 CFET 集成的墊腳石"。

單片式 CMOS CFET:具有挑战性的工藝步驟和模塊

據imec 科學總監 Steven Demuynck 介紹,imec將繼續努力實現單片 CMOS CFET 器件的演示,這是 imec 的一個战略項目,通過與合作夥伴的密切合作得以實現。與單極 CFET 器件不同的是,堆疊的 p-bottom 和 n-top 器件現在將在同一晶圓上實現,並獨立接觸。

此外,集成流程應允許在共用一個柵極的兩個器件上區分閾值電壓 (Vt) 設置-,所有這些都與 50 納米的行業相關柵極間距有關。這種垂直架構具有重大意義。它不僅需要开發三個新的 CFET 專用工藝模塊,還需要調整工藝流程中的其他模塊,以適應這些 CFET 專用模塊的存在。

第一個 CFET 專用工藝模塊(imec稱之爲中間介質隔離 (MDI:middle dielectric isolation ))源於在頂部和底部柵極之間建立垂直介質隔離的需要,以區分頂部和底部器件的 Vt 設置。爲此,imec的團隊提出了一種從一开始就會影響工藝流程的獨特解決方案:將爲創建 CFET 有源部分而形成的硅/硅鍺堆棧轉化爲較高的硅/硅鍺1/硅鍺2 多層堆棧,其中硅鍺2 的 Ge% 要高於硅鍺1。當犧牲的 SiGe1 層被設置 Vt 的工作函數金屬取代時,富含 Ge 的犧牲層被轉化爲 MDI 介電層,從而在柵極內形成 n-p WF 金屬分離。

這種疊層允許在疊層中的缺鍺層上形成內部間隔,這是納米片的一個關鍵特性,可將柵極與源漏極隔離开來。目前,我們研發工作的重點是尋找最有效的方法,在這種狹小間距和高縱橫比幾何形狀下,將底部酸化層、新型 MDI 模塊和內隔板共同集成在一起。

在頂部和底部器件的源極-漏極觸點金屬之間需要第二個垂直隔離。Imec探索了各種方案,以建立和隔離底部和頂部觸點(深入兩個高柵極之間),並隨後布线底部和頂部晶體管。在 2023 年超大規模集成電路會議(VLSI 2023)上分享了一個形態概念驗證流程,展示了制造堆疊 MOL 的能力。

最後,當在底部器件上生長 sourrain 磊晶片時,我們需要封裝頂部溝道。這將有效實現在底部和頂部器件上生長不同摻雜的外延。

Anne Vandooren表示,從長遠來看,imec正在探索從背面連接有源器件的先進集成方案。我們之所以取得這些進展,是因爲需要進一步降低標准單元高度,避免晶圓正面後端线路擁塞。

背面接觸需要額外的工藝步驟,包括晶圓鍵合和從背面減薄基底。這些步驟要求非常緊密的疊加,以便將背面層與正面已有的小特徵對齊。由於晶圓在粘合過程中會發生變形,這就更具有挑战性,需要使用特定的光刻疊層校正方法。此外,還需要一個額外的工藝模塊,以便在背面金屬 1 和 CFET 器件的有源納米片部分之間提供適當的隔離。

行業協作努力

Steven Demuynck表示,自從iemc开始开發 CFET 以來,公司發現與設備供應商的合作越來越緊密。

一方面,這些供應商希望在开發的早期階段就參與進來,以確定他們的工具、工藝和材料在路线圖中的位置。

此外,他們還希望了解這些工具和材料的運行環境,以便在流程的上下遊建立互動意識。Imec 在爲這些公司提供具有 CFET 相關拓撲結構和幾何形狀的硅片方面發揮着關鍵作用。在 IDM 开始开發之前,這些公司通常無法獲得此類材料。

另一方面,這些合作也爲 imec 帶來了好處。與工具供應商的合作有助於我們利用合作夥伴最先進的能力。

與此同時,我們的邏輯核心合作夥伴也有興趣通過評估各種流程來確定我們遇到的關鍵挑战和潛在障礙。在早期階段了解哪些硬件和工藝是可行的,可以爲他們开展研發工作提供先機。

標題:向下一代晶體管邁進

地址:https://www.iknowplus.com/post/38099.html