天價EUV光刻,何去何從?

數十年來,在摩爾定律推動下,半導體行業一派向好。

隨着工藝制程不斷發展,台積電、三星、英特爾等晶圓代工廠商之間的競爭已進入先進制程賽道。在此過程中,EUV極紫外光刻設備成爲各廠商爭奪的焦點。

據報道,2024-2025年,台積電將接受60台EUV光刻機,預估總費用將超122億美元;英特爾率先擁抱全球第一台High NA EUV光刻機;三星也在向High NA EUV光刻機躍躍欲試,試圖追趕台積電。

EUV光刻機遭爭搶背後,各晶圓大廠同樣有苦難言。其中,高昂的光刻機費用,對半導體廠商而言無疑就是一種巨大的負擔。

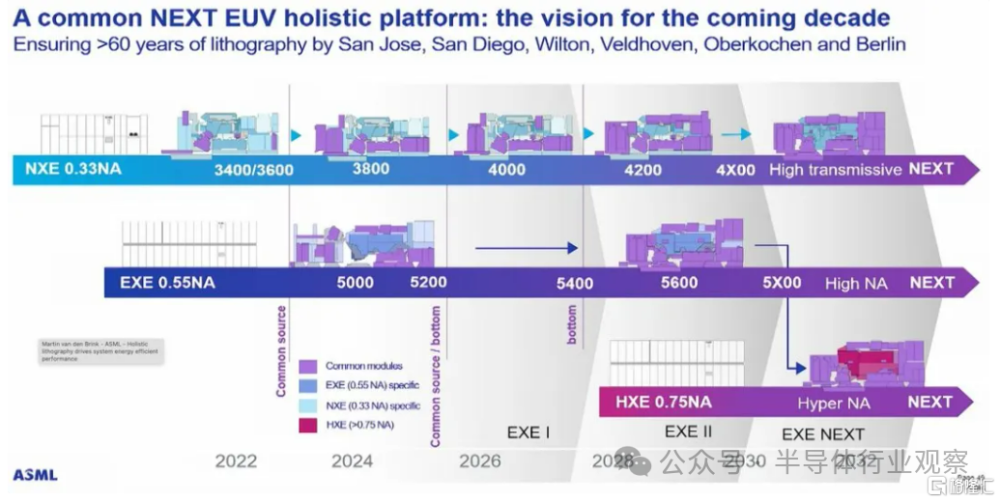

據悉,目前0.33NA EUV光刻機的售價約爲1.81億美元每台,新一代的High-NA(0.55NA) EUV倍增至2.9-3.62億美元一台。而進入1納米以下的埃米世代後,ASML將計劃推出更先進Hyper-NA(0.75NA)EUV光刻機設備,其售價則有可能超過7.24億美元。

ASML光刻機路线圖

在此價格壓力下,一度讓台積電、三星、英特爾等半導體晶圓代工廠商望而卻步。

例如2023年英特爾代工業務虧損70億美元,其採用下一代EUV光刻機而造成成本負擔便是原因之一;台積電也曾多次指出下一代EUV設備價格太貴,甚至表示A16先進制程節點並不一定需要High NA EUV;而困於良率瓶頸的三星,在如此高昂的設備成本面前同樣十分掙扎,在其SF1.4節點的宣傳中甚至都未提到High NA。

可見,設備成本問題已成爲各先進制程代工廠規劃未來工藝時的重要考慮因素。

在此背景下,“降本”與“替代”成爲擺在EUV光刻機面前的兩個選擇。

EUV光刻降本,多路出擊

FEL,替代EUV-LPP光源

EUV光刻機之所以如此昂貴,其中一個關鍵原因在於EUV光源的生產,採用的是目前地球上最強大的商用激光器,通過轟擊金屬錫滴來產生13.5nm EUV光源。

ASML當前所採用的激光等離子體EUV光源(EUV-LPP)光源價格昂貴,效率低下,光電轉化率僅爲3%-5%。

對此,一個非常規的替代方案正在酝釀中。日本高能加速器研究組織(KEK)的研究人員認爲,如果利用粒子加速器的力量,EUV光源的獲取可能會更便宜、更快、更高效。

實際上很早就有研究人員就看到了使用由粒子加速器產生的稱爲自由電子激光器(FEL)來產生強大的EUV光源的可能性。

FEL利用電子在磁場中的運動產生超強激光,其效率比普通EUV光源高出一倍,能量轉化率超過30%,且擁有成本低、功率大等優勢。在電力消耗方面,FEL光源也要遠低於EUV-LPP光源。

KEK高級光源研究員表示:“EUV-FEL光束的極高功率、窄光譜寬度和其他特性使其適合作爲未來光刻的EUV光源來應用。”

此外,EUV-FEL還可升級爲BEUV-FEL,以使用更短的波長(6.6-6.7 nm)實現更精細的圖案化。它還可以可變地控制FEL光的偏振,以實現High NA光刻。

據悉,目前業界已經設計了一種基於能量回收直线加速器(ERL)的FEL光源用於未來的光刻,並且已經研究和开發了主要組件。FEL光源在EUV功率、升級到BEUV-FEL、High NA光刻的偏振控制、電力消耗和每台光刻機的成本方面具有許多優勢。

EUV-FEL光源被認爲是未來光刻最有前途的光源,應進一步推動其產業化。

應用材料,EUV圖案化的一場革命

爲了幫助芯片制造商繼續縮小設計,同時又不增加EUV雙重圖案化的成本、復雜性以及能源和材料消耗,應用材料與領先客戶密切合作,在去年开發了Centura Sculpta圖案化系統。

基於此,芯片制造商可以打印單個EUV圖案,然後使用Sculpta系統在任何選定的方向上拉長形狀,以減少特徵之間的空間並增加圖案密度。由於最終圖案是由單個掩模創建的,因此降低了設計成本和復雜性,並消除了雙圖案對齊誤差的良率風險。

簡單來說就是,原本需要兩次EUV曝光才能完成的過程,現在借助應用材料公司的 Centura Sculpta圖案化系統,就只需要一次EUV曝光就能完成。

與此同時,EUV雙重圖案化需要許多額外的制造工藝步驟,通常包括CVD圖案化薄膜沉積,CMP清潔,光刻膠沉積和去除,EUV光刻,電子束計量,圖案化薄膜蝕刻和晶圓清潔等。

對於其所取代的每個EUV雙圖案序列,Sculpta系統可以爲芯片制造商提供:

每月生產能力每10萬片晶圓可節省約2.5億美元的資本成本

每片晶圓可節省約50美元的制造成本

每片晶圓節能超過15千瓦時

每片晶圓可直接減少0.35千克二氧化碳當量以上的溫室氣體排放

每片晶圓節水約15升

應用材料資深副總裁暨半導體產品事業群總經理Prabu Raja表示,新的Sculpta系統充分證明了材料工程的進步,可以補強EUV光刻技術,協助芯片制造商最佳化芯片面積和成本,並解決先進芯片制程日益增加的經濟和環境挑战。Sculpta系統獨特的圖案成形技術,結合了應用材料公司在帶狀離子束和材料移除技術方面的深厚專業知識,爲圖案化工程師提供了突破性的創新工具。

TechInsights副主席Dan Hutcheson表示,應用材料公司的新Sculpta系統是圖案化的一場革命,爲芯片制造商帶來了全新的功能。隨着行業不斷突破芯片擴展的極限,我們需要像應用材料公司的圖案成形技術這樣的突破,以提高芯片功耗、性能、面積和成本,同時降低設計成本、能源和材料消耗。

Sculpta是自引入CMP以來晶圓制造中最具創新性的新工藝步驟,受到領先芯片制造商的高度關注,並被選爲大批量邏輯制造中多個步驟的記錄生產工具。

在今年2月,應用材料又新推出了一款新的電子束測量設備,專門用於精確測量採用EUV和新興的High-NA EUV光刻技術的半導體器件的關鍵尺寸,可有效降低光刻工藝的成本。

據悉,該設備被稱爲VeritySEM 10關鍵尺寸掃描電子顯微鏡(CD-SEM)測量系統。

據應用材料公司稱,與傳統CD-SEM相比,該設備能夠以較低能量實現2倍分辨率,並提升30%的掃描速度。該設備領先的分辨率和掃描速率改進了對EUV和High-NA EUV光刻和蝕刻工藝的控制,以幫助芯片制造商加速工藝开發並最大限度地提高大批量制造的產量。

“VeritySEM 10是CD-SEM技術的一項突破,它解決了未來幾年將塑造行業的重大技術變化帶來的計量挑战,”應用材料公司成像和過程控制集團副總裁Keith Wells說,“該系統獨特地結合了低着陸能量、高分辨率和更快的成像速度,有助於爲High-NA EUV、GAA晶體管和高密度3D NAND鋪平道路。”

東京電子,應對EUV雙重圖案化挑战

東京電子推出了Acrevia工具,這是一款新型氣體團簇光束 (GCB) 系統,專爲細化EUV光刻創建的圖案而設計。

該工具採用低損傷表面處理,可用於多種用途,包括減少即將推出的節點的EUV多重圖案化使用量、增強线邊緣粗糙度以降低性能變化、減少隨機光刻缺陷,並最終降低芯片制造成本並提高產量。

衆所周知,標准的單次EUV圖案化工藝流程包括八個關鍵步驟:晶圓沉積、化學機械拋光清潔、光刻、計量、圖案蝕刻、清潔、計量和晶圓蝕刻。除了晶圓蝕刻外,所有步驟均重復進行,以進行雙重圖案化。

然而,雙重圖案化 EUV 技術帶來了新的挑战,包括成本增加、良率可能下降以及生產周期延長。東京電子建議在光刻圖案化和隨後的幹蝕刻步驟之後將其Acrevia工具插入工藝技術流程中,而不是雙重圖案化。如果需要,Acrevia工具也可以用於雙重甚至三重EUV圖案化之後進行改進。

雖然Acrevia工具不會取代雙重或三重EUV圖案化,但它可以減少其使用量並改進圖案,從而提高性能和良率,這意義重大。

此外,由於EUV光刻技術會產生隨機效應,這些效應會導致隨機橋接缺陷和較差的线邊緣粗糙度等問題。由於這些缺陷具有隨機性,因此很難檢測到。即使使用EUV雙重圖案化,也無法完全消除這些缺陷。東京電子表示,其圖案細化工具可以改善圖案側壁的线邊緣粗糙度 (LER) 並減少隨機光刻缺陷,從而提高良率。

總結來看,Acrevia採用了東京電子原創技術,可實現高蝕刻速率和低損傷圖案化。在日益具有挑战性的先進圖案化領域,Acrevia使進一步擴大規模成爲可能,並最大限度地提高了生產率。

EUV光刻,替代危機

極紫外光(EUV)光刻技術是目前最先進的光刻技術,它可用於制造制程小於7nm的芯片,但也面臨着技術難、成本高、工藝復雜、供應鏈封閉等問題與挑战。

因此,許多研究機構和企業都在探索其他的先進制程技術,嘗試挑战ASML在超精細制程芯片制造設備方面一家獨大的地位。

納米壓印技術(NIL)

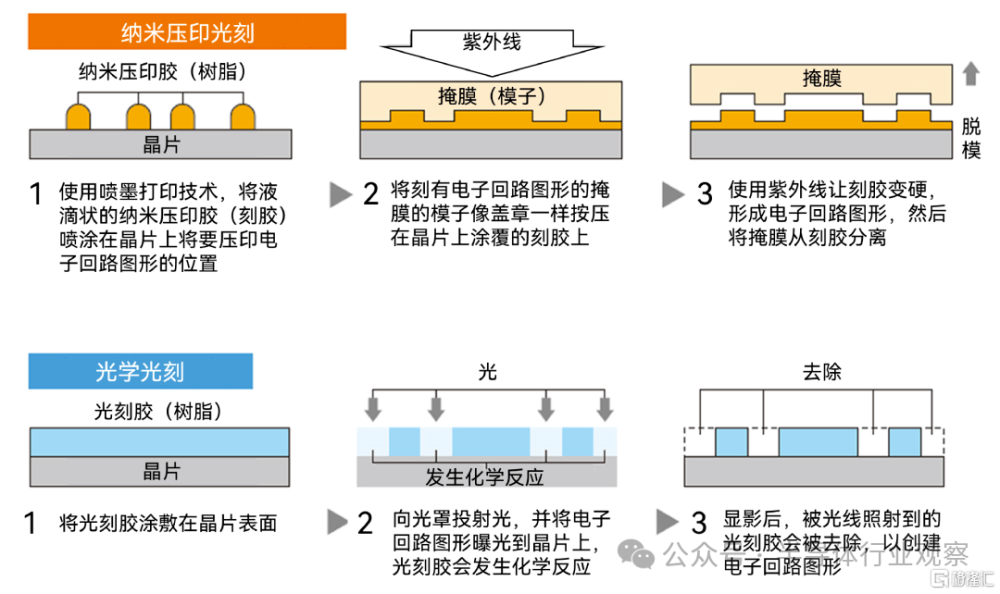

納米壓印(NIL)技術是將印有電路圖案的掩模壓印在晶圓表面的抗蝕劑上,通過類似於印章的形式制造集成電路,將掩模上的精細電路圖案轉移到晶圓上,可在單個壓印件中形成復雜的二維或三維電路圖案。

紫外納米壓印光刻與光學光刻流程對比

可以理解爲,納米壓印技術造芯片就像蓋章一樣,把柵極長度只有幾納米的電路刻在印章(掩膜)上,再將印章蓋在橡皮泥(壓印膠)上,實現圖形轉移後,然後通過熱或者紫外线光照的方法使轉移的圖形固化,以完成微納加工的“雕刻”步驟。

筆者在此前文章《納米壓印,終於走向台前?》中曾寫到,與傳統的光刻技術相比,首先,納米壓印技術不需要復雜的光路系統和昂貴的光源,可以大幅降低制造成本。

另外,納米壓印的模板比光刻機用的掩膜版圖案設計更簡單,壓印出來的圖案尺寸完全由模板上的圖案決定,所以不會受到傳統光刻膠技術中光源波長、光學衍射的限制和影響。與光刻設備產生的圖案相比,納米壓印技術忠實地再現了更高分辨率和更大均勻性的圖案。

同時,納米壓印技術只要預先在掩膜上制作好圖案,即使是復雜結構也能一次性形成,同時也避免了傳統光刻工藝中的多次重復曝光,進一步提升了成本優勢。據日經中文網報道,納米壓印能省掉成本巨大的光刻工序的一部分,與極紫外光刻相比,能將該工序的制造成本降低4成,耗電量降低9成。

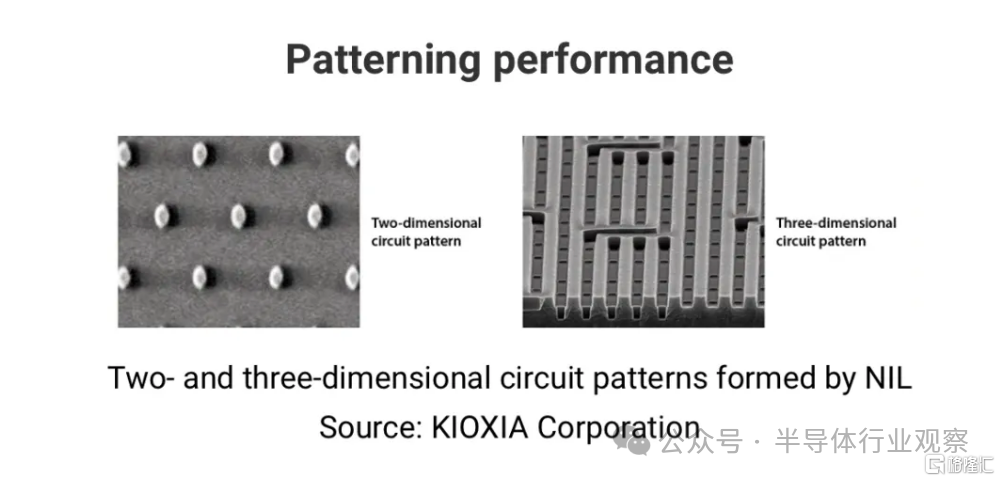

此外,納米壓印技術在三維立體結構加工方面有着它獨特的優勢,傳統的光刻技術都是基於二維平面的加工方式,三維結構獲取比較困難,同時可控性較差,但是對於納米壓印技術,只要制作成模板,就可以批量生產三維產品。

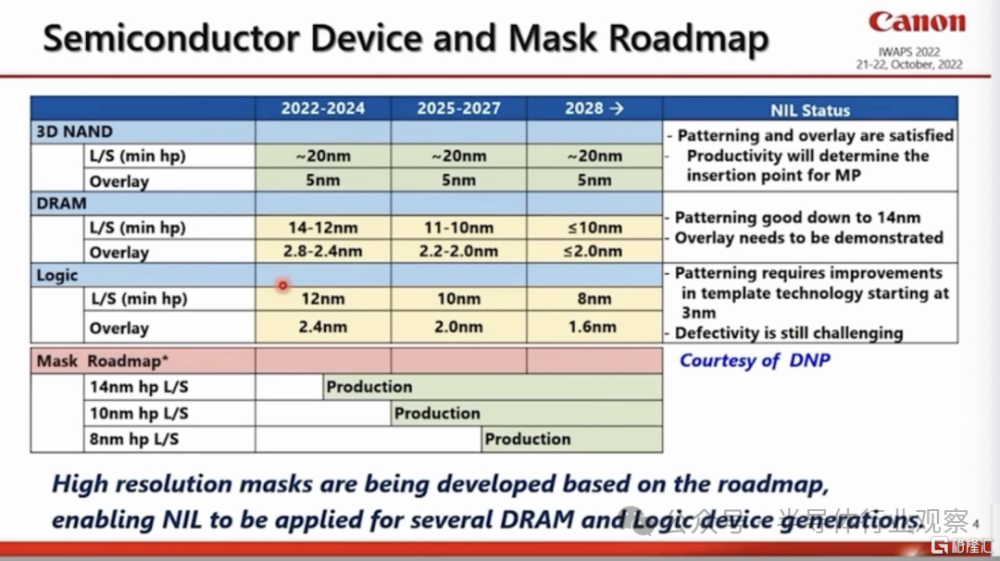

2023年10月,日本佳能公司宣布推出納米壓印芯片制造設備,目前可實現最小线寬爲14nm的圖案化,約等於5nm工藝節點;未來有望實現最小线寬爲10nm的電路圖案,相當於2nm工藝節點。目前,日本鎧俠公司已經將NIL技術應用到了15nm NAND閃存器上,並有望在2025年推出採用NIL技術的5nm芯片。

近日有消息披露,SK海力士從佳能引進了納米壓印設備,目前正在進行測試,計劃在2025年左右使用該設備开始量產3D NAND閃存,到目前爲止的測試結果良好。另一存儲巨頭三星同樣开發了包括納米壓印技術在內多種方案以解決多圖案工藝導致的成本上升問題。

除了在NAND閃存領域的探索外,佳能還正在嘗試將NIL技術應用到DRAM和CPU等邏輯芯片上。

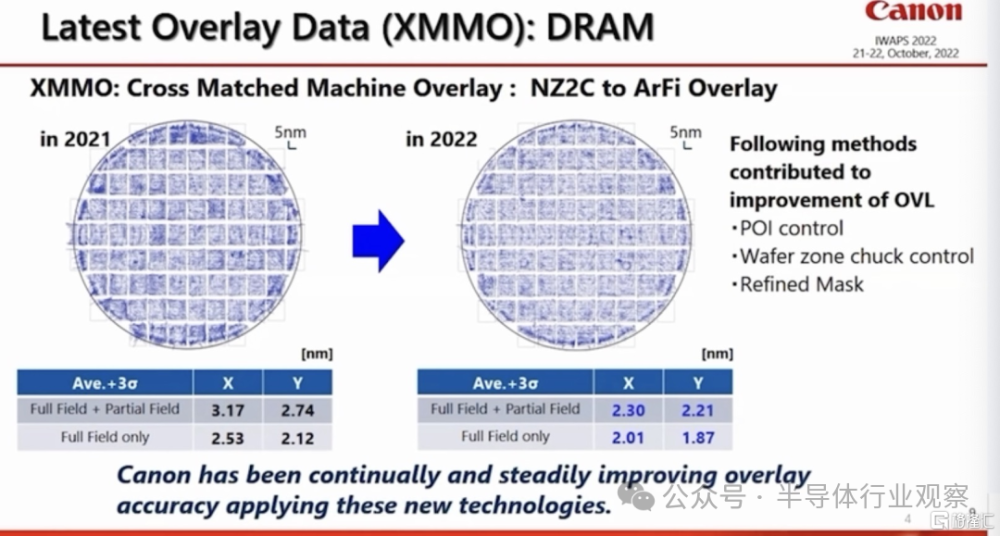

針對DRAM方面,佳能一直在不斷改進套刻精度。使用POI 控制技術、晶圓區卡盤控制、精細掩膜等方式有助於改善套刻精度。

圖源:佳能

高級的NIL工具和掩膜相結合可以爲許多不同的應用提供多種解決方案,佳能展示了2.3nm套刻精度應用於各種新技術,主要用在DRAM方面。

在芯片領域,納米壓印光刻更擅長制造3D NAND、DRAM等存儲芯片,與微處理器等邏輯電路相比,存儲制造商具有嚴格的成本限制,且對缺陷要求放寬,納米壓印光刻技術與之較爲契合。

據佳能在納米壓印設備未來路线圖顯示,應用將從3D NAND存儲芯片开始,逐漸過度到DRAM,最終實現CPU等邏輯芯片的制造。

圖源:佳能

經過近30年的研究,納米壓印技術已經在許多方面有了新進展,國內外半導體設備制造商、材料商以及工藝商紛紛开始涉足這一領域。

尤其是以佳能爲代表的日企,欲通過半導體“納米壓印技術”來追趕ASML的腳步。

據TechNavio數據顯示,2026年納米壓印市場有望達到33億美元,2021年至2026年年復合增長率可達17.74%,該市場雖然沒有想象中那樣大,但整體正逐漸走強。

那么,納米壓印技術能否替代EUV光刻呢?

老實來講,難度是非常大的,其實從行業動態也能看到,每隔幾年都會有納米壓印光刻即將突破的消息,但每次又延後進入產業的時間。

目前納米壓印技術還存在模板缺陷和套准等問題,需要時間才能成熟地進入市場,但其超高分辨率、易量產、低成本、一致性高等優點已經很突出,是最有機會代替現有光刻技術的技術手段之一。在未來光學光刻難以向前演進時,納米壓印技術或將是一條值得期待的光刻路线。

定向自組裝光刻(DSA)

定向自組裝光刻(DSA)是一種利用材料自身的分子排列規律,誘導光刻材料在硅片上自發組成需要的圖案的方法,它比傳統光刻分辨率更高,加工速度也不受影響,但它對材料控制的要求特別高。

IMEC、麻省理工學院等機構都建立了自組裝產线,研究它的具體工藝。基於DSA技術,研究人員提出一種金屬二硫化物晶體管自生長技術,可將二維半導體晶體管尺寸縮小到目前的千分之一大小,且功耗也只有目前的千分之一。

DSA 技術於 1990 年代首次提出,並於 2007 年成爲 ITRS 路线圖的一部分。DSA 的主要支持者是 IMEC 的一個研究小組。2021 年,IMEC展示了使用 DSA 形成 18nm間距线圖案。據了解,DSA光刻尚未被任何主要半導體代工廠用於大批量生產。在過去的二十年裏,這項技術進行了大量的研發和專利活動,但還沒有商業用途。

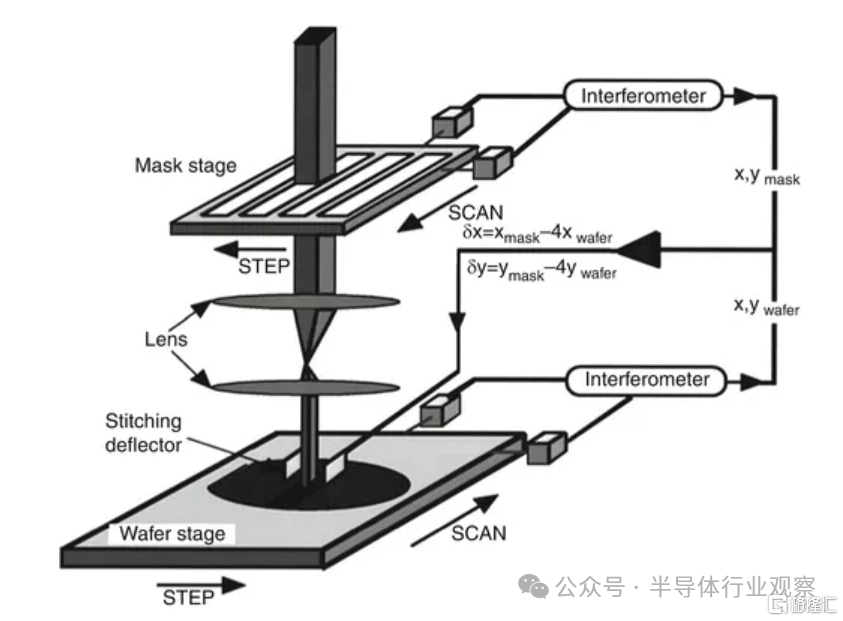

電子束光刻(EBL&MEBL)

電子束光刻(EBL)是一種利用高能電子束來替代光源,直接在硅片上雕刻圖案的方法,它的分辨率相比於EUV光刻更高,但制造速度很慢,只能逐步刻畫,不適合大規模量產。目前它主要用在量子計算芯片、超表面芯片等高精度小批量芯片中。

電子束光刻原理圖(圖源:SpringerLink)

在此基礎上,業界還推出了MB Platform——全球首創的多柱電子束光刻,該技術將以新的生產力優勢徹底改變了電子束光刻 (EBL),同時實現了高分辨率、精細特徵、寬視野和大景深。

實際上,早在20 世紀 80 年代,IBM就开發出了這種直寫光刻技術。從原理上看,多光束直寫利用加速電子束在塗有電子束敏感光刻膠的基板上刻畫出小於 10 納米的特徵。暴露在電子束下會改變光刻膠的溶解度,從而能夠通過將光刻膠浸入顯影劑中來選擇性地去除光刻膠的暴露或未暴露區域。

因爲不需要昂貴的光掩模,直寫技術很有吸引力。但單光束電子束光刻的吞吐量太慢,對於批量 IC 生產來說成本太高。分析人士也直言,直寫真正的問題是吞吐量。直接寫入光刻技術,即使有數十萬甚至一百萬個光束,但對於晶圓光刻來說也太慢了。

因此,單光束直寫工具只能用於復合半導體和光子學等小衆應用。包括KLA,Mapper在內的早期參與者,退出的退出,被收購的被收購。

Multibeam首席執行官兼董事長David K. Lam在接受採訪時表示,希望憑借MEBL技術,復興這項已有幾十年歷史的技術。這就像擁有印刷機或3D打印機的速度,但又具有鉛筆的定制靈活性和適應性,Multibeam可以使芯片制造的某些部分的生產效率比現有系統高出100倍。

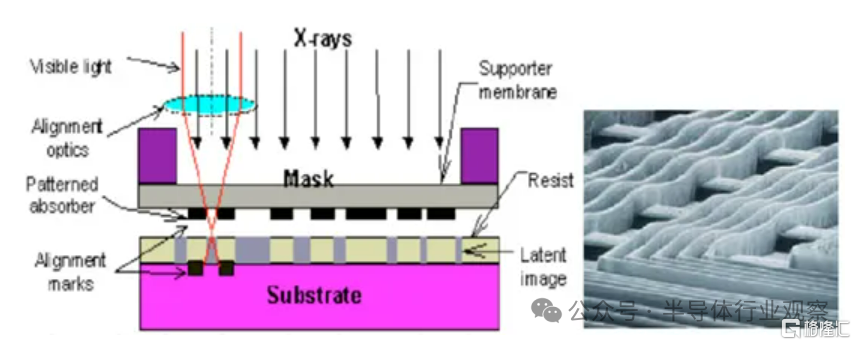

X射线光刻技術(XIL)

X射线的波長很短,幾乎沒有衍射效應,早在二十世紀八十年代就進入了光刻技術研發的視野內。

九十年代,IBM在美國佛蒙特州建了一條採用同步輻射光源的X射线光刻機爲主力的高頻芯片生產线。當年X射线光刻技術,是當時的下一代光刻技術的強有力競爭者。但隨着准分子激光和氟化鎵(GaF)透鏡技術的成熟,深紫外光(DUV)光刻技術得以發展,在分辨率和經濟性上優於X射线光刻。

近年來,俄羅斯重新提出使用X射线進行無掩膜的直接光刻,來制造7nm的芯片,目標是在2028年實現大規模量產。

X射线光刻原理圖(圖源:Advances)

寫在最後

摩爾定律本質上是一個經濟規律。

在一個抽象的層面上,摩爾定律並不單單綁定某一個具體技術。過去幾十年,半導體公司把芯片產品分發到更大的市場,把產品的研發生產費用分攤到更大的基數上,以提高單品的利潤率。然後,再把利潤投入到技術升級,晶體管小型化,性能提高,再進一步降低單品價格,因爲價格降低又發現了更多更大的應用市場,如此不斷良性循環。

如果從更長遠的歷史視角看,按照未來學家 Ray Kurzweil 的話說,摩爾定律只是幾百年來,人類的計算技術——從算盤到手搖機械計算機再到繼電器、真空管、晶體管,進而到大規模集成電路的演變——在過去五十年的自然體現。

時至今日,隨着芯片制程微縮接近物理極限,EUV光刻設備價格飛速飆升,摩爾定律的經濟規律正在被打破。

人們曾多次預言EUV光刻技術將被其他技術所替代。在以下的年份,甚至認爲繼任者已經准備就緒:

1972年Spears和Smith提出的X射线光刻技術(XRL);

1980年飛利浦公司开發的電子束圖案生成器(EBPG);

1995年Chou提出的納米壓印光刻技術(NIL);

2000年Kruit等人在Mapper公司开發的電子束並行寫入技術;

2010年提出的X射线幹涉光刻技術(XIL)。

EUV光刻替代技術的不斷進步正推動半導體領域的快速進步。受到成本與效率的雙重考量,以及近期半導體供應鏈安全問題的迫切壓力,各國有十足動力开發EUV光刻的替代方案。

然而盡管這些替代技術均呈現出巨大的潛力,但它們仍需深入的研究和改進,以解決技術成熟度和商業化方面的挑战。這一過程將爲半導體產業提供新的發展機遇,推動技術的不斷演進與升級。

標題:天價EUV光刻,何去何從?

地址:https://www.iknowplus.com/post/127064.html