這一封裝技術,要崛起了

後摩爾時代,從晶圓代工廠、封裝廠、IDM到IC設計公司,都开始將先進封裝作爲突破摩爾定律的一個方向。

據分析機構Yole預計,2028年先進封裝市場規模將達786億美元,2022-2028年的年復合增長約10%,顯示出巨大的發展潛力。

其中,扇出型面板級封裝(FOPLP)作爲先進封裝技術發展的一個重要分支,正在頻頻進入人們的視野。

近日,有消息傳出,AI芯片龍頭英偉達最快將於2026年導入扇出型面板級封裝,借此緩解CoWoS先進封裝產能喫緊,導致AI芯片供應不足的問題,英特爾、AMD等半導體大廠後續也將逐步加入扇出型面板級封裝的陣營。

這一舉動或將打破當下CoWoS在AI芯片先進封裝獨霸的局面。

AI的風,吹到了FOPLP市場

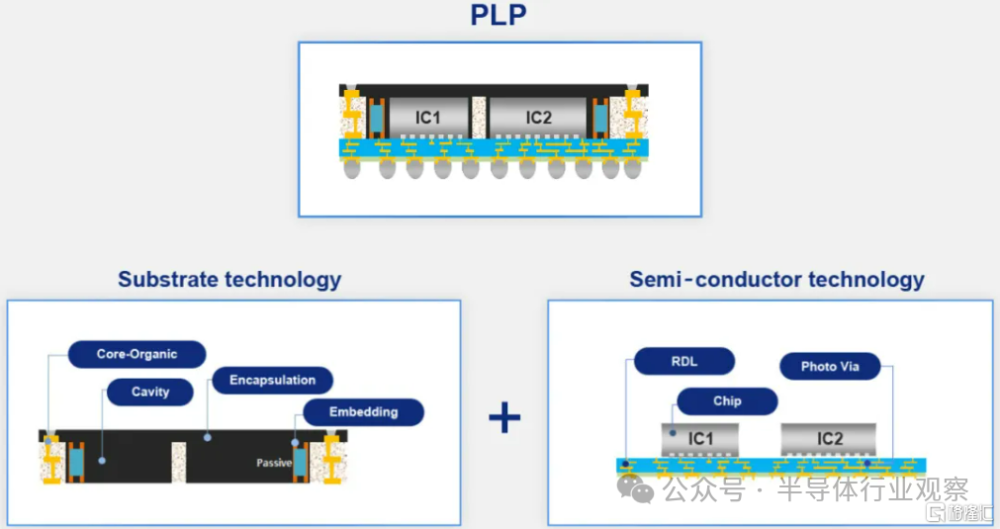

扇出面板級封裝是基於重新布线層(RDL)工藝,將芯片重新分布在大面板上進行互連的先進封裝技術,能夠將多個芯片、無源元件和互連集成在一個封裝內。FOPLP與傳統封裝方法相比,提供了更大的靈活性、可擴展性和成本效益。

扇出型面板級封裝可以理解爲扇出晶圓級封裝的延伸,是在多晶粒集成的需求,加上進一步降低生產成本的考量下,所衍生而出的封裝技術。

因此,扇出型板級封裝具備顯著的效能提升和成本降低優勢。其高面積利用率有效減少了浪費,同時能夠在一次封裝過程中處理更多的芯片,顯著提高了封裝效率,形成強大的規模效應,從而具有極強的成本優勢。

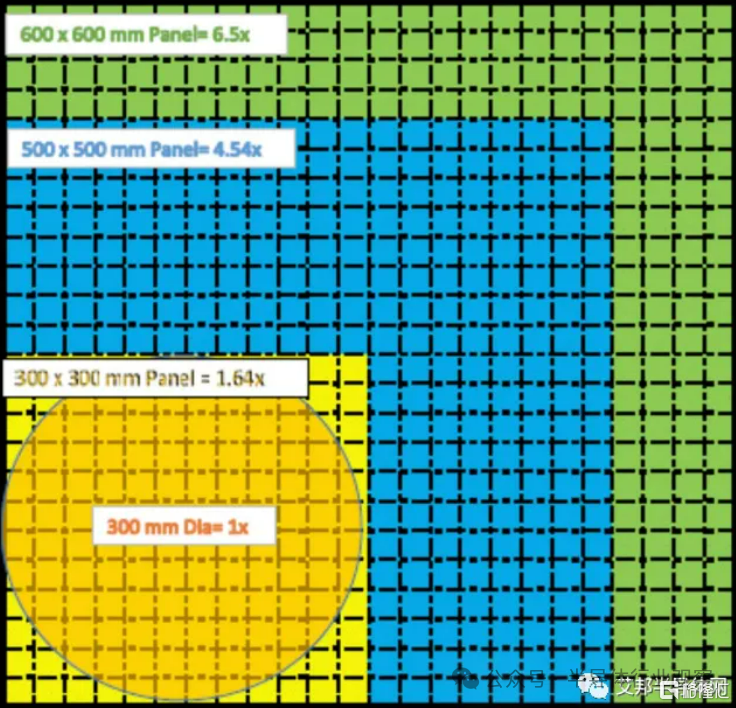

據Yole的報告顯示,FOWLP(扇出型晶圓級封裝)技術的面積使用率<85%,FOPLP面積使用率>95%,這使得300mmx300mm的面板比同尺寸12英寸的晶圓可以多容納1.64倍的die,這導致生產過程中生產速率的差異。

晶圓級封裝上出現的Partial DIE(Edge缺陷DIE)將不會在面板級封裝中出現

(圖源:艾邦半導體網)

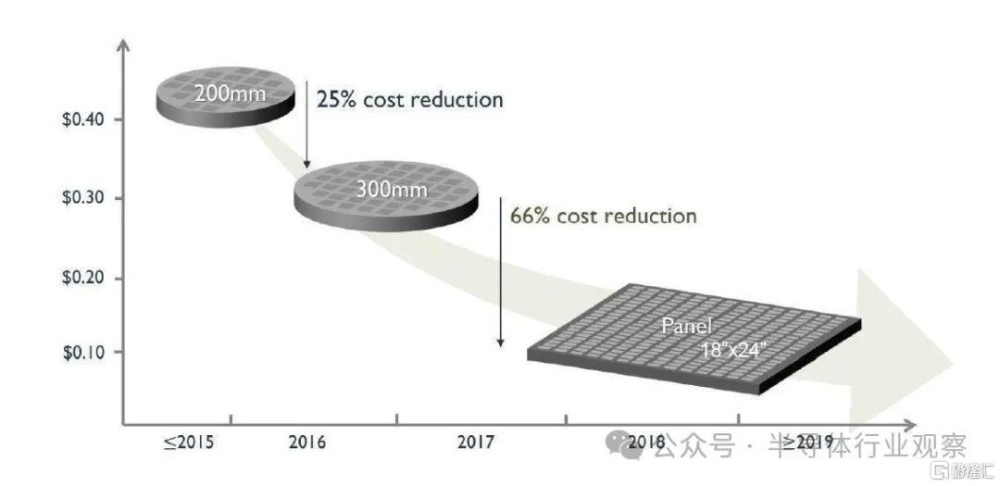

同時,隨着基板面積的增加,芯片制造成本逐漸下降。從200mm過渡到300mm大約能節省25%的成本,而從300mm過渡到板級封裝,則能節約高達66%的成本。

圖源:Yole

綜合FOPLP的各項優勢來看,英偉達、AMD、英特爾等AI芯片大廠導入扇出型面板級封裝,除了希望借此緩解CoWoS先進封裝產能喫緊,導致AI芯片供應不足的問題之外。

另一方面,主流廠商也試圖嘗試利用FOPLP封裝技術降低成本,彌補先進制程芯片研發和制造成本不斷上升的困難。

蘇州晶方半導體副總經理劉宏鈞給筆者算了一筆账,以英偉達的H100爲例,它是在CoWoS-S(硅基)上封裝的7個芯片,中心是814平方毫米的H100 GPU芯片,圍繞它的是6個堆疊的HBM內存芯片。H100每季度的出貨量高達400000個且供不應求,據報道台積電2023年初的CoWoS產能還不到每月10000片,而到年底可能已經突破了20000片/月,據傳台積電會繼續增加相關產能至40000片/月,以應對AI芯片大廠的需求。這些產能的80%會被英偉達和AMD消耗,後續隨着GB200等新產品的熱賣,以及其他廠商例如博通對CoWoS的需求,台積電的產能確實已經有了被擠爆的危險,短時間內不會有任何緩和的跡象。

因此,尋找某種其他的方案來解決產能已經是過去至少一年來行業的共同認知,這確實爲FOPLP封裝帶來了新的機遇。

“由於其工藝尺寸原因,FOPLP技術指標弱於台積電的CoWoS-S,但其潛在優勢是成本和產能瓶頸突破的可能性。這些因素促使目前CoWoS的用戶努力尋找替代技術。” 劉宏鈞補充道。

盡管弱於CoWoS技術,但相較於其它傳統封裝技術,FOPLP以其卓越的I/O密度和電氣性能,成爲滿足AI計算需求的關鍵所在。

通過RDL工藝,FOPLP技術能夠實現高帶寬、高密度的D2D互連,這一特性在AI計算中尤爲關鍵,能夠有效滿足數據傳輸與處理的迫切需求。

不僅如此,FOPLP技術在提升芯片功能密度、縮短互聯長度以及進行系統重構等方面均展現出顯著優勢,這恰好符合AI時代對芯片性能提出的基本要求。

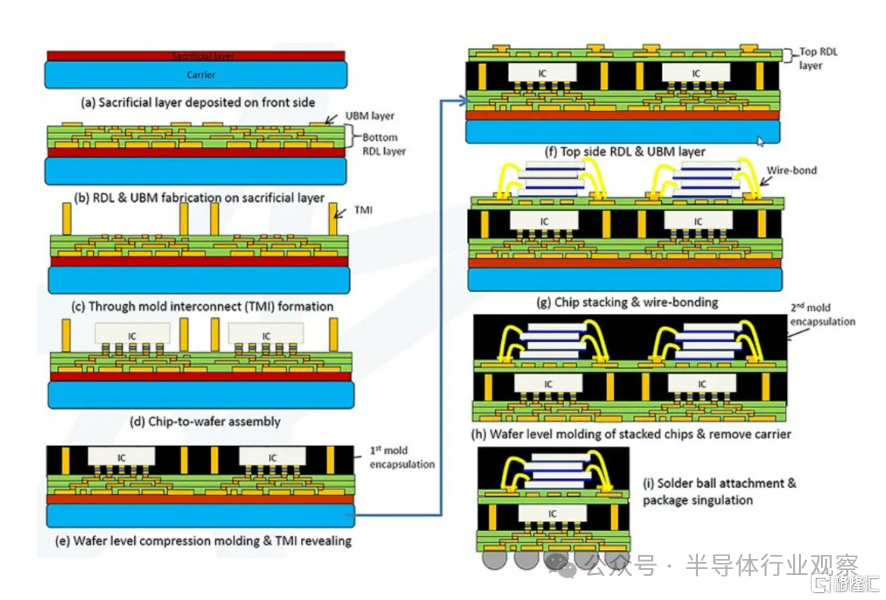

圖源:未來半導體

芯和半導體聯合創始人代文亮博士表示,從人工智能發展的需求和走勢來看,高性能計算芯片引入面板級扇出型封裝技術是大致確定的路线選擇。盡管該技術短期內無法替代CoWoS,但未來在封測市場的份額比重會逐步增加,以解決當前有機基板和硅基板接近極限,無法滿足高端芯片需求的瓶頸問題。

綜合來看,AI計算的需求增長、先進封裝技術的發展、成本效益的考量、技術創新的推動、市場需求的多樣化等,這些因素共同促成了FOPLP技術的異軍突起。

據Yole數據顯示,2022年FOPLP的市場空間大約是11.8億美元,預計到2026年將增長到43.6億美元。可以預見,FOPLP技術具備巨大的成長潛力。

“嗅到” FOPLP商機

廣闊的市場前景下,OSAT、IDM、Foundry、基板制造商等一衆廠商,都已“嗅到”商機,近年來都在積極投入發展FOPLP這一先進封裝技術,進一步證明了市場對FOPLP技術的廣泛認可和高度期待。

根據麥姆斯咨詢早些時候發布的報告顯示,三星電子、力成科技、日月光、群創、華潤微、奕斯偉、中科智芯、Nepes和雲天半導體等正在利用現有設施和工藝能力,投資面扇出型板級封裝技術,以實現規模經濟生產。

以三星電子爲例,2015在與台積電競爭Apple手機處理器訂單失利後,三星電子對先進封裝技術給予了高度關注,其成立的特別工作小組攜手三星電機成功开發出面板等級扇出封裝技術,並與台積電研發的InFO-WLP技術一較高下,成爲第一家進入量產的面板級封裝廠商。

圖源:三星

這一努力在2018年實現了一個新的裏程碑,三星在其Galaxy智能手表上採用了最新的扇出型面板級封裝APE-PMIC,這是FOPLP的全球首次量產。

最初,FOPLP主要用於移動應用。2020年开始的5G、AI、自動駕駛和服務器需求導致對模塊化和高速數據處理的需求急劇增長。

因此,兼顧性能和成本驅動優勢的FOPLP技術可以滿足多芯片封裝方面的這些需求,已經逐漸拓展到諸多應用領域。

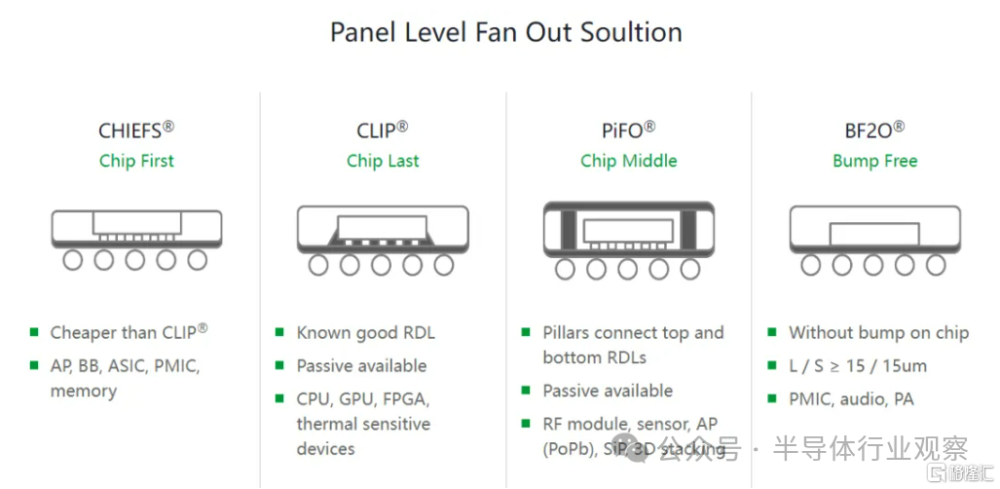

劉宏鈞向筆者指出:“高端扇出封裝需求主要來自於同時需要晶體管數量和通訊帶寬的應用領域,例如FPGA、某些Networking管理芯片等。由於I/O密度,良率和成本的因素,這些扇出封裝一般都是以Chip-last的形式存在。除了這些高端扇出封裝外,還有一些中低端的扇出以Chip-first的形式存在,以實現更高密度的封裝集成,應用在例如Sensor、射頻芯片、電源芯片、WiFi/音頻等產品上。”

值得關注的是,如汽車中約有66%的芯片可以使用FOPLP封裝技術進行生產,是汽車芯片生產的出色解決方案。

在此趨勢帶動下,力成、群創、日月光等上述廠商逐漸結合自身的工藝能力投資扇出型板級封裝技術的量產。同時國內一些IDM、封裝廠也开始提前布局FOPLP。

例如,力成科技在2018年打造了全球第一座使用扇出型面板級封裝制程的量產基地,正式布局高階封裝領域,已成功運用於聯發科PMIC和音頻收發器上。

圖源:Powertech Technology

日月光也是最早布局面板級扇出型技術的領導廠家之一。於2019 年底產线建置完成,2020 下半年量產,應用在RF、FEM、Power和Server領域。2022年日月光推出了VIPack先進封裝平台,提供垂直互聯集成封裝解決方案。VIPack就是以3D異質整合爲關鍵技術的先進互連技術解決方案,建立完整的協同合作平台。

群創光電首度提出一項前所未有的概念——Panel Semiconductor,以業界超大尺寸G3.5 FOPLP (620mm X 750mm) Glass Panel,开發线寬介於2μm-10μm的中高階半導體封裝,爲客戶提供更有競爭力的技術和利潤價值。

在頭部大廠的帶動下,中國大陸扇出面板級封裝廠商正在乘勝追擊,已經量產或具備生產能力。

中科四合:深圳中科四合致力於爲AI、通信、汽車、工業、消費類等多個領域提供高性能、高可靠性的功率芯片及模組解決方案。中科四合是國內最早將大板級扇出封裝(FOPLP)技術量產於功率芯片/模組的供應商之一,公司產品涵蓋多種二極管、MOSFET、GaN、電源模組等功率芯片/模組。中科四合在深圳龍華區和廈門海滄區均設有制造工廠,2017年已規模量產。針對功率芯片及模組產品定義,中科四合基於基板溼法工藝全新开發了一套板級扇出封裝工藝和生產线,可實現低成本、高散熱、大電流、三維集成、低寄生參數的功率芯片/模組解決方案。

奕成科技:奕成科技是國內板級高密封裝技術領域的領先者,主要從事板級系統封測集成電路業務,載板尺寸爲510mmx 515mm,技術平台可對應2D FO、2.xD、3D PoP、Embedded Die四大板級系統集成技術方案,在芯片偏移控制、翹曲度、RDL等核心工藝指標上已達行業領先水准。2023年4月,奕成科技高端板級系統封測集成電路項目點亮投產,標志着其首座板級高密系統封測工廠正式進入客戶認證及批量試產階段。

矽磐微電子:華潤微電子於2018年成立矽磐微電子(重慶)公司從事面板級封裝業務,面板級封裝技術有效解決了Chiplet封裝成本高昂的問題,更適用於功率類半導體封裝異構集成化。

矽邁微電子:合肥矽邁微電子建成了國內首條具備量產能力的基板扇出封裝生產线,並率先完成工藝开發,客戶認證和試驗量產,量產產品包括電源管理類,射頻類,系統模塊等。

佛智芯微電子:廣東佛智芯微電子結合現有半導體制程工藝設備和後道載板制程工藝裝備的優勢,打造了半加成法扇出封裝先進的线路創成工藝(i-FOSATM),具備工藝先進 、成本合理、供應鏈安全的特性,建設國內首條高性價比板級扇出型封裝研發线和示範线,旨在打通Chip-First、Chip-Last、3D/SiP核心工藝。同時,爲增加板級封裝技術創新與合作,佛智芯通過建立“板級扇出封裝創新聯合體”,打造產業鏈共性平台,聯合體成員包含亞智、華爲、華進等40多名國內外企業。

天芯互聯:天芯互聯爲深南電路全資子公司,同樣擁有FOPLP平台,爲客戶提供高集成小型化的半導體器件模組封裝解決方案和半導體測試接口解決方案。

...

此外,扇出型面板級封裝發展還需要更多廠商的參與和投入:

在面板級封裝光刻機領域,日本佳能動作非常快,佳能在錯失超紫外光刻機的機遇後,不會再放過任何一個機會。

在面板級封裝RDL工藝領域,Manz是領跑者之一,2016年Manz开始進軍半導體先進封裝領域,面板尺寸目前已能做到業界最大的700mm x 700mm面板,並克服了面板翹曲問題。

在面板級晶粒貼裝領域,ASMPT、華封科技、華芯智能、深科達等都有相應產品,基本可以滿足大多數封裝產品的需求。

另外,考慮到芯片、封裝與PCB的同步設計及同步研發越來越重要,FOPLP的發展也需要PCB廠、載板廠、面板廠等這些後段封裝廠的協同努力。一方面有助於上述企業利用既有經驗快速切入FOPLP技術,另一方面,前後段半導體產業的共同投入也有助於尋找到最具競爭力的生產成本、提升產品競爭力的路徑。

對PCB廠、載板廠來說,發展FOPLP的優勢是通過制程知識和設備升級、改造,逐漸向前段制程跨進,快速跨入先進封裝技術市場。

而處於半導體產業鏈上遊的EDA,同樣也在密切關注FOPLP行業的變化與市場機會。代文亮博士指出,在EDA方面,芯和半導體能夠爲FOPLP封裝設計提供一站式多物理場仿真EDA解決方案,通過完全自主知識產權,大規模跨尺度的仿真引擎,AI加持的自適應網格剖分和分布式並行計算等核心能力,幫助用戶解決信號完整性、電源完整性、電磁兼容、電熱和盈利給可靠性等方面的問題,加速產品开發和迭代。

無論如何,隨着產業鏈上下遊廠商的不斷關注和入局,有望推動扇出型面板級封裝市場空間的進一步增長。

FOPLP封裝,仍挑战重重

盡管FOPLP封裝技術开始嶄露頭角,業界已有廠商實現了FOPLP產品的量產。

但總體來說,目前FOPLP產業的發展還不夠成熟,因受到良率產量、供應鏈不完善、面板翹曲及設備投入研發、標准化問題、散熱等種種挑战,整個行業尚處於相對早期的階段,產業發展進程仍有待提高。

以設備爲例,由於面板級封裝是全新的封裝技術,也需要新的封裝設備加以支持。比如貼片機就是產线改造中最重要的環節之一。由於面板級封裝使用的載板尺寸更大,表面容易凹凸翹曲,對應機台尺寸也就更大,Pick & Place動作的路徑更長,對機台的效率、運動機構的一致性、穩定性都提出了更高的要求。

此外,面板級封裝與當前晶圓級封裝數據系統不完全兼容,需要對原有產线進行改造。面板級封裝還需要RDL制造設備,开發特殊的檢測及測量工具以及激光/熱釋放層、介質層材料等,這需要大量的前期投資來打造完整的產業生態鏈。這也是爲什么台積電、英特爾至今也沒有大肆开發扇出型面板級封裝。

有專家指出,面板級封裝設備的开發需要廠商在硬件和算法上具有較強的協同能力,這樣才能從底層上去解決問題。

另外,面板級封裝設備廠商還應具有一定的模塊化平台架構設計能力,這樣才能使設備產品具有高度靈活性和可轉換性,做到全工藝、全尺寸覆蓋,幫助客戶更好地適應先進封裝領域快速的發展變化,產能可快速在不同工藝需求的產线進行調配,工藝轉換成本也更低。

板級封裝的難點還在於設備供應商沒有統一規範,面板尺寸沒有通用標准。主要原因是因爲當前需求量還較低,設備供應商沒有太大的熱情來冒險开發整條產线。

總的來說,要想充分釋放FOPLP這一技術的潛力,行業必須正視並克服貼裝精度、芯片偏移、翹曲和光刻等諸多挑战,對設備和標准的持續投資與發展亦不可或缺。

市場份額上,過去數年FOPLP一直處於爬坡階段,在整體封裝市場佔比較小。

但相信隨着英偉達、AMD、英特爾等芯片大廠的轉向,未來將有望充分釋放FOPLP封裝的技術優勢和市場需求,爲行業發展注入新動力。

標題:這一封裝技術,要崛起了

地址:https://www.iknowplus.com/post/105036.html