大廠競逐先進制程

最近,先進半導體工藝制程方面的消息有不少。就在過去一周,相關的新聞包括:

聯發科宣布率先完成3nm工藝的下一代SoC的开發,打破了蘋果最先使用下一代工藝制造手機SoC的慣例

Intel CEO預期將在2025年借助18A工藝來追上甚至超越TSMC和三星在先進制程領域的領先位置,目前已經有大客戶支付了大額預付款來使用該工藝

Intel預計將在未來兩年內繼續大量使用TSMC工藝來生產最先進的處理器產品(Meteor Lake及後續產品),在未來兩年Intel估計會使用超過150億美元來使用TSMC的工藝

Intel和三星正在合作开發下一代內存-處理器堆疊產品(cache DRAM),該技術作爲對AMD的3D V-Cache的回應,將DRAM直接堆疊在CPU上,從而大大提升系統的集成度和性能

三星在美國的4nm工廠預計在2024年底完成,超過TSMC在美國建廠的速度

從這些消息,我們可以看到的是,首先,隨着以人工智能爲主力的新需求漸漸推動半導體市場漸漸復蘇,對於先進制程產能的需求非常旺盛,而晶圓制造廠對於擴大先進制程產能也抱着積極的態度。而在另一方面,全球範圍內幾大瞄准先進制程的巨頭目前的競爭格局也很清楚:TSMC是先進制程領域的領跑者,其良率和性能都能領先一步達到較高的水准,同時TSMC還擁有全球領先的先進封裝技術,因此憑借這樣領先的綜合地位領跑整個先進制程市場,大客戶紛紛在TSMC下單導致產能無法滿足需求。

三星是先進工藝領域的有力競爭者,隨着其技術成熟度與TSMC逐漸接近以及TSMC產能緊張,未來預計也會獲得先進制程領域的大量訂單。而Intel則是先進工藝領域的新進競爭者。Intel在最近才真正進入先進制程的競爭有兩重原因:第一是因爲Intel之前在10nm工藝節點的开發中拖延了太久,導致其技術在過去幾年中大大落後與TSMC和三星;但是隨着Pat Gelsinger成爲Intel CEO位置後進行大刀闊斧的改革,目前Intel在先進工藝技術領域與TSMC和三星的差距已經在快速縮小,預計在未來兩年內有機會能真正和TSMC/三星同步推出最新工藝制程。第二個原因是Intel在Pat Gelsinger執掌CEO之後正式決定大規模投入晶圓代工領域,從而與TSMC和三星真正开始直接競爭(而在這之前Intel並不大規模开放自家工藝,因此和TSMC/三星並沒有直接競爭關系)。

我們在先進半導體制程看到了樂觀的市場預期和火熱的競爭;但是,在競爭之外,幾大晶圓制造廠之間也有合作關系,這就讓這些公司之間的關系變成更加微妙的競爭-合作關系。例如,Intel目前最主要CPU業務线中,還必須依靠TSMC。在Intel的Meteor Lake中,預計GPU tile會使用TSMC的工藝,而CPU則使用Intel自己的工藝。另一方面,Intel也在和三星合作內存堆疊技術(cache DRAM)以追趕AMD在這方面的領先地位。

先進封裝帶來的變化

過去20年間,芯片設計行業的主流設計範式是SoC。SoC設計方法給芯片行業帶來了極大的繁榮,但是在先進制程時代,這樣的設計方法會由於先進封裝技術而發生改變,而這樣的改變也會對先進制程晶圓制造廠的競爭合作關系帶來改變。

在SoC設計方法中,SoC芯片由許多IP組成。芯片設計公司在設計SoC時,首先定義需要SoC上需要的IP,並且從第三方IP提供商處獲取IP或者自己設計IP;然後把這些IP集成到芯片上,最後把整個SoC送到晶圓制造廠中進行流片制造。

在SoC設計方法中,芯片設計公司更多的是關注SoC系統以及每個IP的設計,但是在芯片制造的時候,所有的IP都會使用同樣的工藝去制造,而不可能對於不同的IP使用不同的工藝去制造。

而隨着先進工藝和先進封裝的發展,這樣的SoC設計方法正在慢慢被芯片粒(chiplet)設計方法取代。先進工藝的成本很高,良率卻並不容易做高,爲了提高良率,通常的方法是把大芯片分成多個芯片粒,並且使用高級封裝技術做芯片粒之間的整合。目前,AMD、Intel等都已經在最新的處理器產品中使用這樣的芯片粒設計,預計未來芯片粒設計將會成爲更多使用先進制程的大型芯片的選擇。

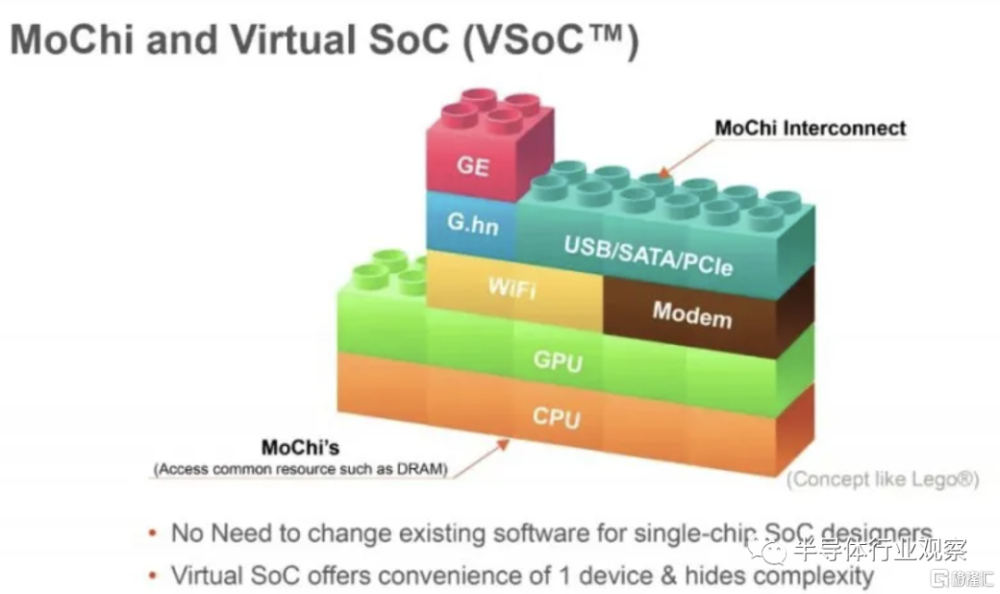

而一旦SoC設計方法慢慢被芯片粒設計方法所取代,SoC設計方法中“整個SoC都要使用相同半導體工藝制造”的假設也就不再成立,因此每一個芯片粒都可以使用不同的工藝來制造。正如2015年Marvell在ISSCC上提到的MoChi概念一樣,整個基於芯片粒的設計把整個芯片系統拆分成了多個芯片粒,每個芯片粒都可以使用最適合的工藝來制造,並且最終整合在一起。

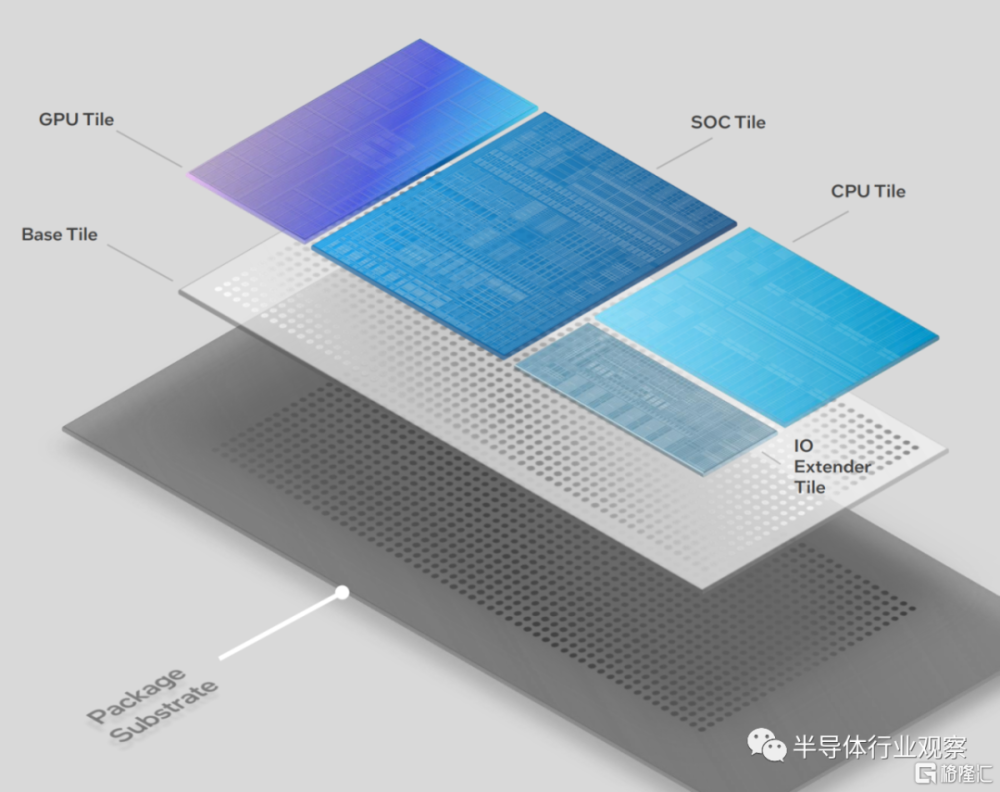

我們在Intel的Meteor Lake中就看到了這樣的設計。在Meteor Lake中,分成了多個芯片粒(Intel稱之爲“tile”),包括CPU Tile,GPU Tile,SOC Tile和IO Tile等,這些不同的Tile都可以用不同的工藝制造並且最後使用高級封裝技術集成在一起。在Meteor Lake中,CPU Tile使用Intel的工藝,而GPU Tile則會使用TSMC的工藝。

差異化將是未來演化方向

當使用先進工藝的芯片設計方法逐漸從SoC轉向芯片粒,晶圓制造廠未來的訂單也可望逐漸從整個SoC慢慢轉向單獨的芯片粒。芯片設計廠商可以選擇最適合的晶圓制造廠去制造相應的芯片粒並且最後集成到一起。芯片粒設計方法加上先進工藝自身的特性,可能會讓未來晶圓制造廠越來越專注於差異化。

先進制程很貴,但是帶來的性能提升並不大。在九十年代摩爾定律的黃金時代,每次工藝節點縮小都可以實現晶體管性能幾乎翻倍;而在目前,每一代工藝演進帶來的晶體管性能提升僅僅在10-20%左右。可以想像,芯片設計公司在大成本投入先進工藝制造芯片後,也必然希望這樣的高投入能獲得盡可能大的回報,因此希望可以在芯片粒的顆粒度上實現每個芯片粒的性能最佳。

而在另一方面,由於先進工藝研發難度巨大,且研發成本投入巨大,因此不太可能出現一家晶圓制造廠在性能、功耗、成本等領域全方位大幅領先其他晶圓制造廠的情況,更有可能是在不同的設計領域,不同的晶圓廠各有所長,從而實現差異化競爭。這裏的差異化,既包括了在性能、功耗、成本等指標維度的區別;也包括了不同的廠商擅長不同領域的芯片粒,例如TSMC擅長高性能計算,三星擅長存儲相關領域等。

在這樣的情況下,不同晶圓廠差異化競爭,都各有自己擅長的方向,而芯片設計公司則各取所長,使用不同的晶圓制造廠去做最擅長領域的芯片粒並且最後整合在一起,可能就是未來的新競爭格局。Intel的Meteor Lake中,GPU Tile使用TSMC制造,就是因爲TSMC擅長高性能計算芯片粒;而CPU Tile使用Intel的工藝制造,也是因爲Intel在CPU領域的工藝-芯片協同設計有着幾十年的積累。未來Meteor Lake這樣的不同晶圓廠制造不同芯片粒可望會成爲主流,而這也會讓晶圓廠走差異化競爭的道路。

先進封裝將是先進制程競賽中的核心競爭力

如前所述,芯片粒設計方法將大大改變晶圓制造廠在先進制程領域的競爭格局,而在上述分析中,不應忽視的是先進封裝技術也將成爲一個重要變量,因爲先進制程芯片(尤其是高性能計算芯片)離不开先進封裝技術。而且更關鍵的是,先進封裝技術在未來將會和先進制程越來越緊密地結合,而掌握這些先進封裝技術的也恰恰是TSMC、Intel和三星這樣的先進制程晶圓制造廠,而不是第三方封測廠。

在未來,先進封裝的重要性甚至不亞於先進制程的優化能力,未來的晶圓制造廠競爭力將會取決於半導體工藝和先進封裝技術的綜合。例如,目前TSMC能獲得Nvidia H100 GPU訂單的一個重要因素,就是因爲TSMC同時擁有最先進的4nm半導體制造工藝以及CoWoS先進封裝技術,而目前H100供不應求事實上是被CoWoS產能所限制,而不是4nm半導體工藝產能所限制。事實上,由於先進封裝和先進制程供貨商互相重合,晶圓制造廠甚至有可能利用其在某一方面的優勢來撬動市場(例如,利用其在先進封裝領域的優勢來彌補其在某個領域先進制程上的劣勢來獲得訂單)。

展望未來,TSMC目前雖然同時擁有先進封裝和先進工藝方面的領先地位,但是Intel在EMIB等先進封裝技術上已經有很久的技術積累,隨着Intel在先進半導體工藝追趕,未來兩者結合會有相當的競爭力;而Samsung的I-Cube/H-Cube和X-Cube等先進封裝技術可望也會在SoC/內存集成領域有自己獨特的優勢。未來的先進工藝晶圓廠之間的競爭格局遠未塵埃落定,值得我們關注。

標題:大廠競逐先進制程

地址:https://www.iknowplus.com/post/31512.html