背面供電技術,越來越熱!

當今時代,半導體行業的競爭可謂白熱化,台積電、三星和英特爾等巨頭都在爭相展示3nm、2nm先進工藝的技術突破。這場超精細晶體管制造競賽的背後,是對芯片工藝制程新時代的追逐,以及摩爾定律極限的挑战。

GAA、High-NA、先進封裝等一系列創新技術,在爲摩爾定律續命之余,越來越多的研究者近年來开始關注起一個新的技術方向——晶圓背面供電(Backside power delivery networks ,BSPDN)。

與EUV光刻機類似,BSPDN被視爲繼續开發更精細工藝節點技術的基本技術,預計將成爲領先芯片晶圓廠的又一個競爭高地。

近日,韓國芯片巨頭三星宣稱要積極布局背面供電網絡技術,並宣布將此導入邏輯芯片的开發藍圖。同時,英特爾、台積電等晶圓制造大廠也都在積極布局背面供電技術。

那么,受到業界大廠廣泛追捧的背面供電技術是什么?將在摩爾定律中起到什么作用?

詳解背面供電的優勢與價值

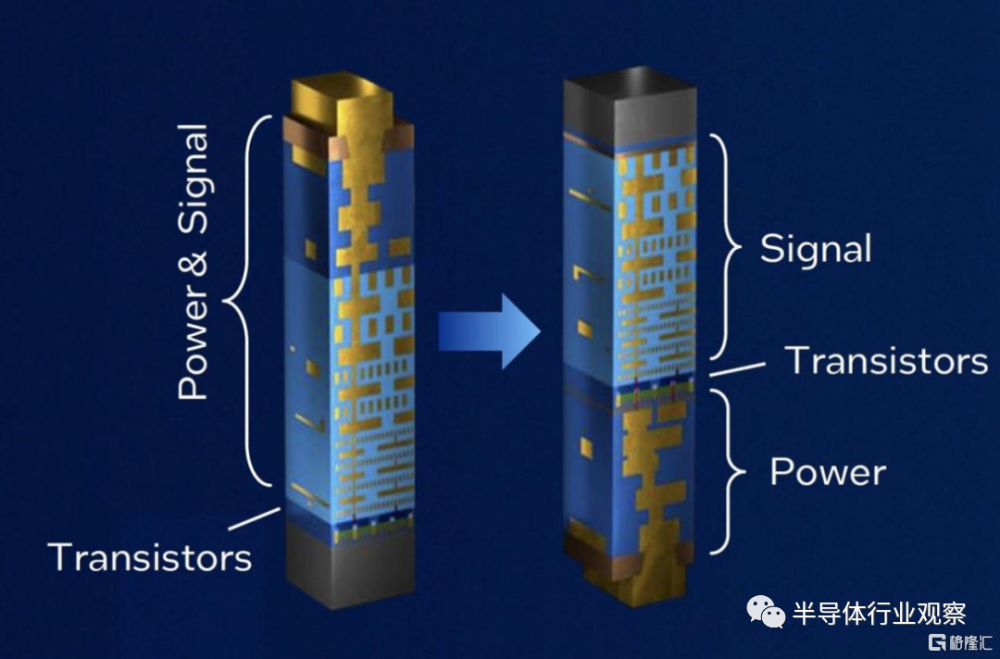

過去多年來,芯片制造從最小的元件——晶體管开始,然後需要建立越來越小的线路層,用於連接晶體管與金屬層,這些线路被稱爲信號互連线,當中還包括給晶體管供電的電源线。當芯片的裸片制造完成後,還需要把它翻轉並封裝起來對裸片進行保護,並提供了與外部的接口,使其真正成爲一個商用化的芯片。

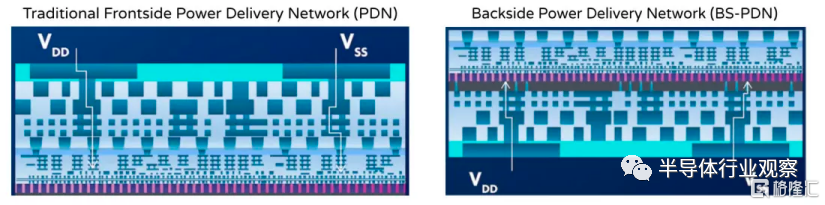

然而,隨着摩爾定律的演進,晶體管越來越小,密度越來越高,堆棧層數也越來越多,可能需要穿過10-20層堆棧才能爲下方的晶體管提供供電和數據信號,導致互連线和電源线共存的线路層變成了一個越來越混亂的網絡。同時,電子在向下傳輸的過程中,會出現IR壓降現象,導致電力損失產生。

除了電力損失之外,PDN佔用的空間也是一個問題。如今芯片內部的電源线路,在布线復雜的後段制程上,往往佔據了至少20%的繞线資源,如何解決信號網絡跟供電網絡之間的資源排擠問題,使元件進一步微縮,變成芯片設計者所面臨的主要挑战之一。

對此,業界开始探索把供電網絡轉移到芯片背面的可能性。

背面供電技術(BSPDN)將原先和晶體管一同排布的供電網絡直接轉移到晶體管的背面重新排布,也是晶體管三維結構上的一種創新,該技術可以在增加單位面積內晶體管密度的同時,避免晶體管和電源網絡之間的信號幹擾,減輕线路後端的布线擁塞並提供電源性能優勢,增強芯片的可靠性。

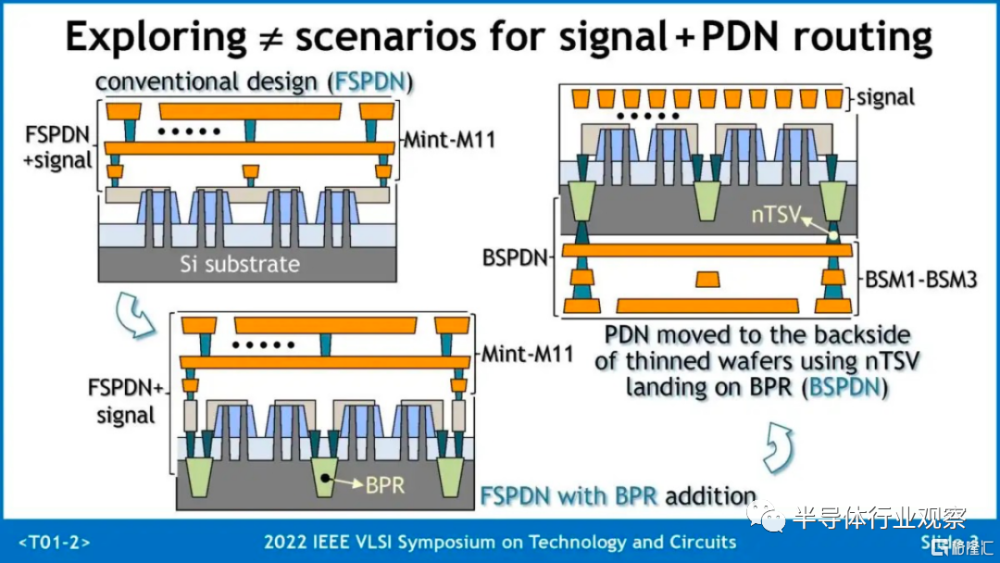

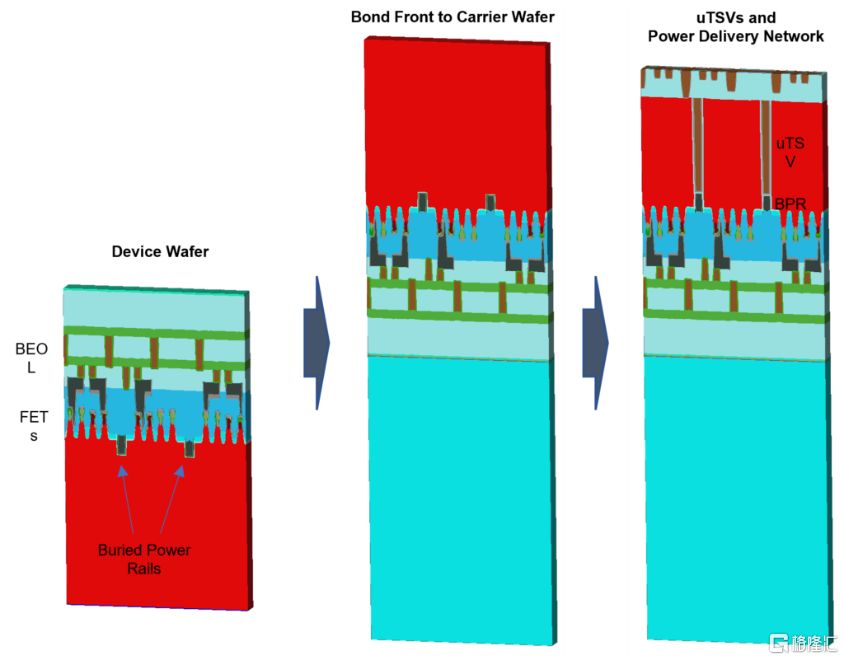

背部供電技術是一項應用於先進半導體的創新技術,旨在更好地挖掘晶圓背面空間的潛力。但要把PDN從芯片正面轉移到背面,需要兩項關鍵技術,分別是埋入式電源軌(BPR)與納米硅穿孔(nTSV),

晶圓制造過程將先制造正面的晶體管,然後添加互聯層,然後將晶圓反轉,並對背面進行打磨減薄,在通過納米硅穿孔(TSV)技術在晶圓背面進行制造供電網絡,並與埋入式的電源軌連接。

其中,埋入式電源軌是一種微縮化技術,可以進一步降低標准單元的高度,並減緩IR壓降問題。這些電源軌是埋在電晶體下方的導线,一部份藏在硅基板內,另一部份則在淺溝槽隔離氧化層內。它們取代了傳統後段制程在標准單元布下的電源线與接地线。

使用埋入式電源軌進行背面供電

在2019年的IEEE國際電子研究會議上,IMEC攜手Arm預測背面供電技術所能帶來的效能升級。Arm在其开發與採用先進設計規則的CPU上進行模擬,並比較“傳統供電”、“晶圓正面供電結合埋入式電源軌”、“背面供電搭配納米硅穿孔與埋入式電源軌”這三種供電網絡方法的優劣。

Arm研究人員發現BPR本身可以構建一個比普通前端供電網絡效率高40%的電力網絡。就供電效率的結果來看,第三種明顯勝過其它方法,與傳統的正面供電網絡相比,芯片電壓損耗大幅下降7倍。

總結來看,背面供電技術將帶來截然不同的芯片性能提升:

改善物理設計。背面供電可以大幅減少DRC違規和時序擁堵,提高芯片利用率達85%以上。

金屬线長縮減。背面供電在M1-M3層可實現30-50%的金屬线長縮減,這將轉化爲時鐘功耗降低、緩衝器數量減少和主動功耗降低。

IR Droop效應顯著下降。背面供電可以實現更低的電源網格密度,IR降從50mV下降到20mV,大幅改善芯片性能。

系統級指標提升。线長減少和IR降低將帶來時鐘功耗減少15-20%、面積縮減15%的系統級優勢。據稱,與傳統供電技術(FSPDN)相比,BSPDN的性能提高了44%,能效提高了30%。

成本降低。通過將電源分配到背面,下面的金屬層將形成一個更寬松的間距,這意味着可以減少EUV光刻次數,降低成本。

諸多優勢加持下,使背面供電成爲了當前熱門的技術議題。

代工三巨頭,加碼背面供電技術

台積電、三星、英特爾等芯片大廠都在積極布局背面供電網絡技術,並宣布將導入先進邏輯芯片的开發藍圖。

三星BSPDN开發計劃曝光

除了率先向GAA晶體管的轉型外,背面供電技術也是三星追逐先進制程的一個殺手鐗。

據ETNews報道,三星電子代工部門首席技術官Jung Ki-tae Jung在最近舉辦的論壇上宣布“我們計劃在2027年將BSPDN應用於1.4nm工藝”。

根據TheElec和三星在今年VLSI研討會上的演講報告,與傳統的前端供電網絡相比,新的背面供電網絡(BSPDN)方法成功地將所需的晶圓面積減少了14.8%,芯片能擁有更多空間,公司可增加更多晶體管,提高整體性能;同時布线長度減少了9.2%,有助於降低電阻、使更多電流通過,從而降低功耗,改善功率傳輸狀況。

三星電子相關人士表示:“採用背面供電技術的半導體的量產時間可能會根據客戶的日程安排而改變。”三星電子目標是在2025年量產2nm工藝,先於1.4nm工藝。據稱,三星目前正在對背面供電技術的應用進行客戶需求調查。

英特爾先聲奪人

三星並非第一家要採用背面供電技術的芯片廠商。

英特爾顯然也看到了背面供電技術帶來的諸多好處,在BSPDN技術上的推進最爲積極。

英特爾將自家的BSPDN稱爲PowerVia。不久前,英特爾發文介紹了PowerVia背面供電技術,該技術可幫助實現降低功耗、提升效率和性能,滿足不斷增長的算力需求。此外,背面供電技術也提高了設計的簡易性。

在2023年VLSI研討會上,英特爾展示了制造和測試其背面供電解決方案PowerVia的過程,並公布已經有良好性能的測試結果。據介紹,電源线原本可能佔據芯片上面20%的空間,但是PowerVia背面供電技術節省了這一空間,也意味着互連層可以變得更寬松一些。

據了解,英特爾團隊還特地制作了“Blue Sky Creek”測試芯片來證明這種方法,證明通過背面供電技術,電源线和互連线可以分離开來,並做得线徑更大,以同時改善供電和信號傳輸。

測試結果顯示,芯片大部分區域的標准單元利用率都超過90%,平台電壓降低了30%,並實現了6%的頻率增益,同時單元密度也大幅增加,並有望降低成本。PowerVia測試芯片也展示了良好的散熱特性,符合邏輯微縮預期將實現的更高功率密度。

作爲大幅領先競爭對手的背面供電解決方案,PowerVia讓包含英特爾代工服務(IFS)客戶在內的芯片設計公司能更快地實現產品能效和性能的提升。

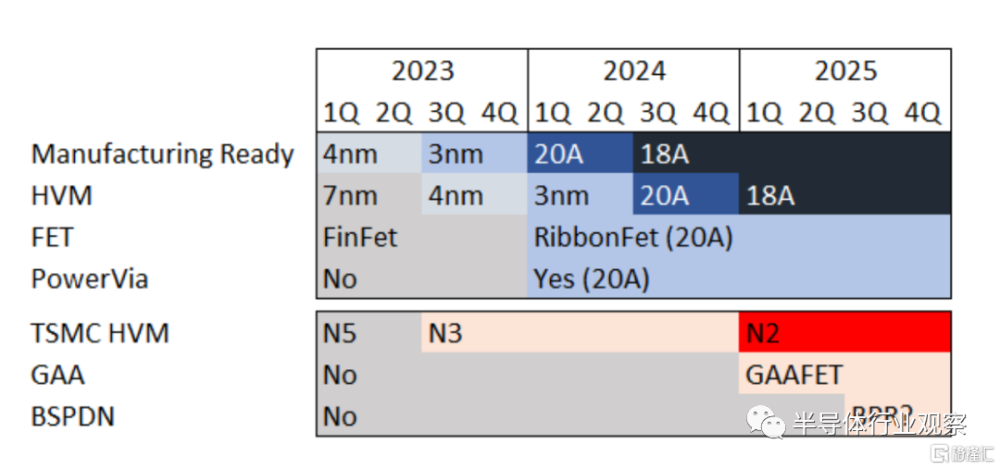

根據英特爾PowerVia背面供電技術的官方介紹,英特爾將在Intel 20A(2nm)將是英特爾首個採用PowerVia背面供電技術及RibbonFET全環繞柵極晶體管(RibbonFET是英特爾對GAA晶體管的實現)的節點,預計將於 2024 年上半年實現生產准備就緒,應用於未來量產的客戶端ARL平台,目前正在晶圓廠啓動步進(First Stepping)。

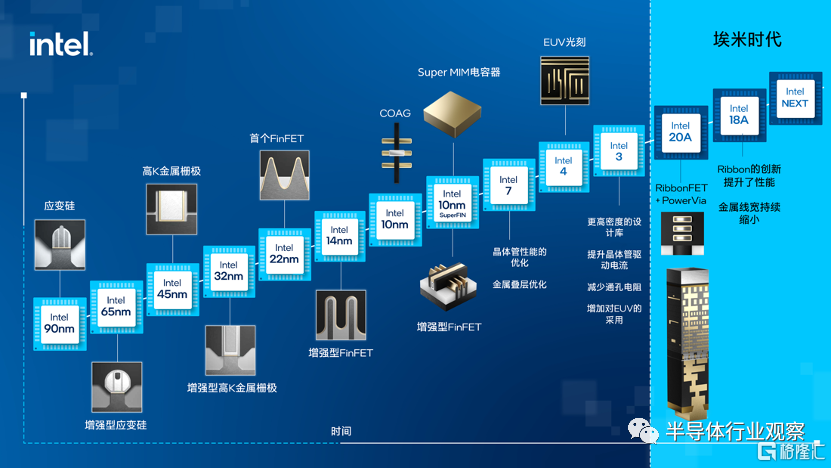

英特爾制程工藝路线圖(來源:英特爾)

這是Pat Gelsinger和英特爾對其架構的一次大膽嘗試。對於英特爾來說,在台積電之前採用PowerVia,通過使用RibbonFET 來做到這一點。這或許是在先進工藝上重新奪回領先的機遇。

屆時,英特爾在芯片設計和制程技術創新方面或將處於行業領先地位。

台積電略顯保守

相對於英特爾來說,台積電對BSPDN技術的應用更加保守。台積電選擇的BSPDN實現方法是一種低復雜度的埋入式電源軌,這種技術成功率比較高,因爲可以在現有的工具上完成。

在台積電2023年技術研討會上,其透露N2P制程將通過背面供電技術減少IR Drop和改善信號,將性能提高10%-12%,並將邏輯面積減少10%-15%。

但關於如何實施背面供電網絡技術,台積電並沒有過多的透露。但台積電曾經介紹過3D IC封裝技術SoIC,這是他們實現背面供電的一個很重要的前提准備。

有市場消息稱,台積電如期2025年上线2nm制程,2025年下半年在新竹市寶山鄉量產,計劃2026年推出N2P制程,這個制程將採用BSPDN技術。

背面供電優勢明顯,挑战仍在

雖然從FSPDN到BSPDN的轉變聽起來很有希望,且優勢明顯,但BSPDN距離真正商用還有一定距離。

真正的背面供電網絡的實現伴隨着額外的技術復雜性。一方面,背面供電技術需要一種專用的晶圓減薄工藝以及處理將器件晶圓背面電連接到正面的納米硅通孔 (nTSV) 的能力。

另一方面,實現晶圓背面電源供應需要在晶圓背面添加金屬層(背面電極),但背面電極的的加工和設計並不像正面那樣簡單,由於背面電極和正面電路之間存在物理和電學障礙,因此必須進行詳細的物理和電學模擬和設計。

此外,背面供電技術還存在調試、散熱和設計等方面的技術挑战。

調試和檢查是BSPDN最有趣的問題之一。英特爾稱其爲“黑天鵝"事件,因爲調試的許多工具都必須從頭开始創建,所有調試工具和EDA設計工具都是爲前端設計而設計的。相關廠商不僅要弄清楚如何生產該工藝,還要弄清楚如何擴展該工藝。

熱管理是另一個巨大的挑战,溫度是人們對背面電源一直擔心的問題之一,因爲晶體管的埋層將更難冷卻,而且層數越多,問題就越多。

三星在研討會上還提出了實施背面供電傳輸模型的最大挑战之一,即與BSPDN相關的拉伸強度可能會降低。在實際應用時,BSPDN可以減少拉應力作用和硅通孔電極(TSV),導致與金屬層分離。

三星表示,這個問題可以通過降低高度或加寬TSV來解決,但在正式宣布解決方案之前需要進行詳細的研究和測試。要成功應用BSPDN技術,還需要在信號和電力线連接方面取得更多進步。除了上述之外,還需要在化學機械拋光 (CMP) 技術方面取得進步,當前的CMP實施用於從晶圓背面去除5-10微米的“峰谷”,而實施BSPDN可能需要一種新的方法來拋光晶圓而不損壞底層功率元件。

寫在最後

背面供電技術的出現,成爲了在下一代光刻機出現之前延續摩爾定律的一大關鍵,芯片突破3nm/2nm的關鍵技術之一。

不難發現,背面供電網絡技術已成爲過去幾年在整個芯片制造行業悄然發展的技術概念,預計未來所有領先的芯片晶圓廠都將轉向該技術。

從目前各企業進展和投入力度來看,英特爾正在領銜出擊,三星和台積電則進度稍慢。

如果英特爾因爲沒有更早使用EUV 失去了對台積電的領先優勢,那么台積電也可能會因爲沒採取積極的設計舉措來提高性能而失去領先優勢。隨着三星的加入,三家在先進制程上競爭的代工廠全部加入了BSPDN的研究,這也意味着BSPDN可能會成爲一個巨大的拐點。

除了晶圓制造公司,上遊的設備公司也在BSPDN領域展开了研究。應用材料公司與BESI合作推出的Die-to-Wafer工具,Tokyo Electron提供了一種新Wafer to Wafer工具。這些市場是巨大的增量增長驅動力,背面供電布线的設備預計將以現在晶圓制造的設備3倍的增長速度增長。

總體而言,BSPDN技術的應用將推動半導體工藝的進一步發展,爲行業帶來更高的效率和性能。英特爾、三星電子、台積電,以及產業鏈企業等都在不斷努力尋求技術突破,以保持在競爭激烈的半導體市場中的領先地位。隨着時間的推移,我們期待看到更多關於BSPDN技術的進展和應用。

標題:背面供電技術,越來越熱!

地址:https://www.iknowplus.com/post/24313.html