代工巨頭“血拼”先進封裝

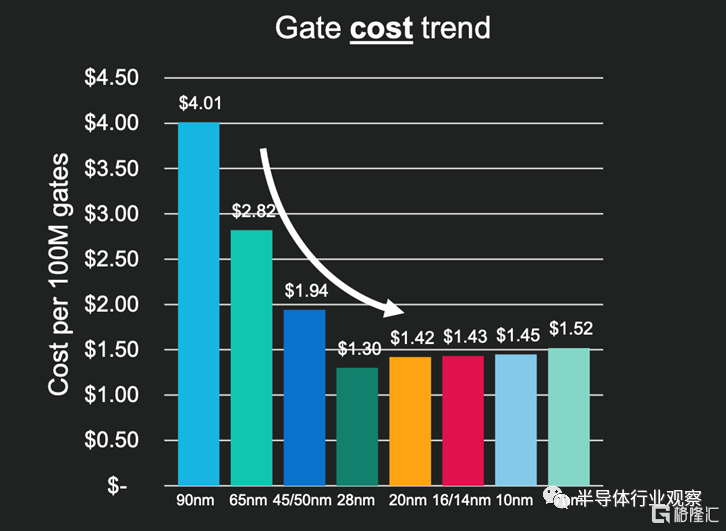

半個多世紀以來,微電子技術大致遵循着“摩爾定律”快速發展。但近年來,隨着芯片制程工藝的演進,“摩爾定律”迭代進度放緩,導致芯片的性能增長邊際成本急劇上升。據IBS統計,在達到 28nm制程節點以後,如果繼續縮小制程節點,每百萬門晶體管的制造成本不降反升。

芯片每百萬門制造成本隨制程節點變化趨勢

(來源:IBS)

而另一方面,在摩爾定律減速的同時,計算需求卻在暴漲。隨着雲計算、大數據、人工智能、自動駕駛等新興領域的快速發展,對算力芯片的效能要求越來越高。

後摩爾時代,在計算需求瓶頸、芯片制造面臨物理極限與經濟效益邊際提升多重挑战下,半導體行業开始探索新的發展路徑。

其中,先進封裝成爲超越摩爾定律方向中的一條重要賽道。

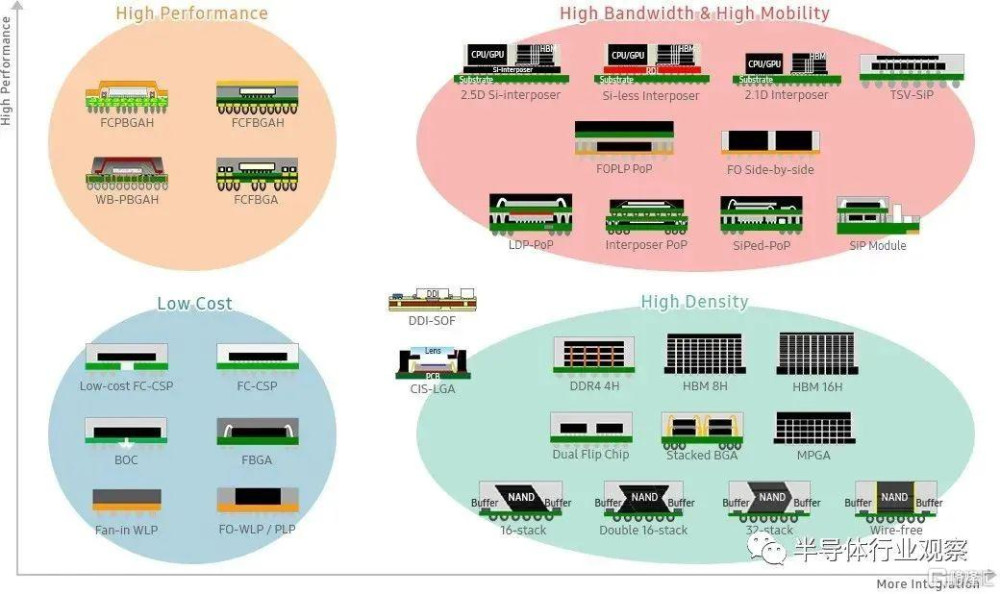

先進封裝在提高芯片集成度、縮短芯片距離、加快芯片間電氣連接速度以及性能優化的過程中扮演了更重要角色,正成爲助力系統性能持續提升的重要保障,並滿足“輕、薄、短、小”和系統集成化的需求。

可見,隨着大算力需求提升,以及單芯片向更先進制程推進難度的增大,先進封裝替代先進制程成爲降低單位算力成本的關鍵方案。

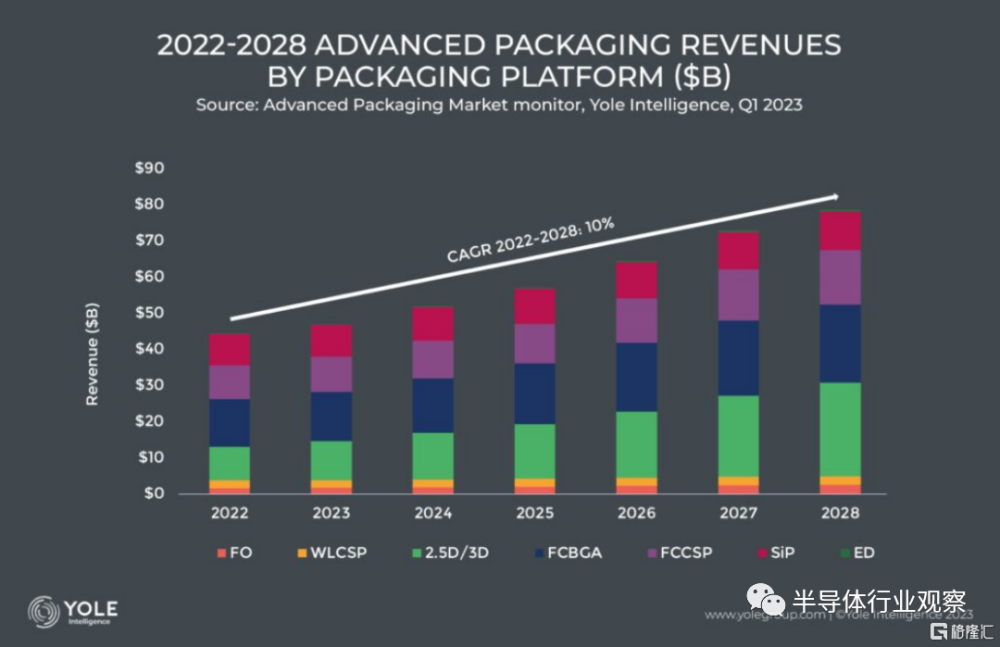

Yole Group最新的Advanced Packaging Market Monitor數據顯示 ,全球先進封裝市場規模將由2022年的443億美元,增長到2028年的786億美元,年復合成長率(CAGR)爲10.6%。

市場潛力之下,前後道頭部廠商紛紛搶灘,積極投資先進封裝技術。

從晶圓代工廠商動態來看,在代工制程按照摩爾定律飛速發展的甜蜜期,封裝並沒有進入晶圓代工廠的視野。然而,近幾年來隨着摩爾定律失速,先進制程的成本快速提升,一些晶圓代工大廠的發展重心正在從過去追求更先進納米制程,轉向封裝技術的創新。諸如台積電、英特爾、三星、聯電等芯片制造廠商紛紛跨足封裝領域,先進封裝技術無疑成爲代工巨頭角逐的重要战場。

代工巨頭發力先進封裝

台積電優勢凸顯

早在10多年前台積電就看出隨着半導體前段工藝的快速微縮,後段封裝技術會跟不上前段工藝的腳步,等到那時,摩爾定律真的會失效。因此毅然決定投入封裝技術,在2008年底成立了導线與封裝技術整合部門(IIPD )。

2009年,彼時在金融危機的背景和影響下,台積電陷入了經營虧損、被迫減薪裁員的困境。與此同時,28nm制程工藝環節,研發成本快速提升;台積電同時還面臨三星、英特爾、格芯以及聯電的強力挑战。

內憂外患下,張忠謀重新出山執掌台積電,同時請回已經退休的蔣尚義掌舵研發,开發先進封裝技術進行差異化競爭。

2011年秋,CoWoS的技術負責人余振華帶來了第一個產品——CoWoS。

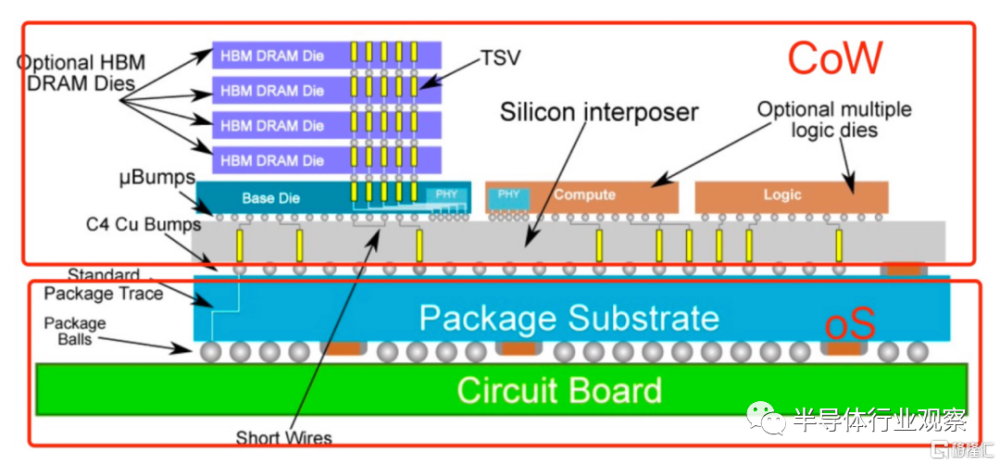

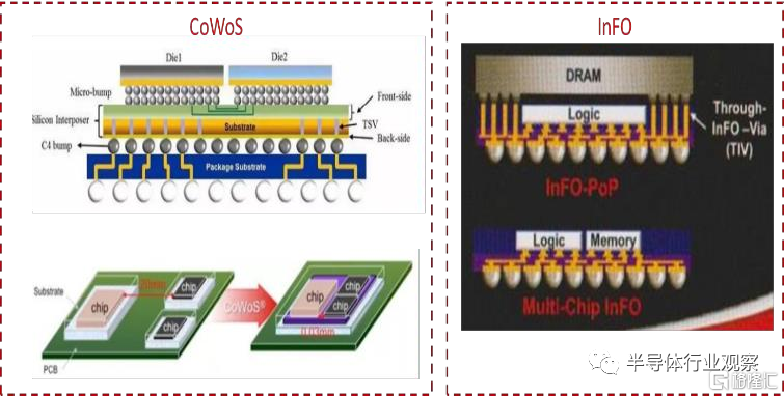

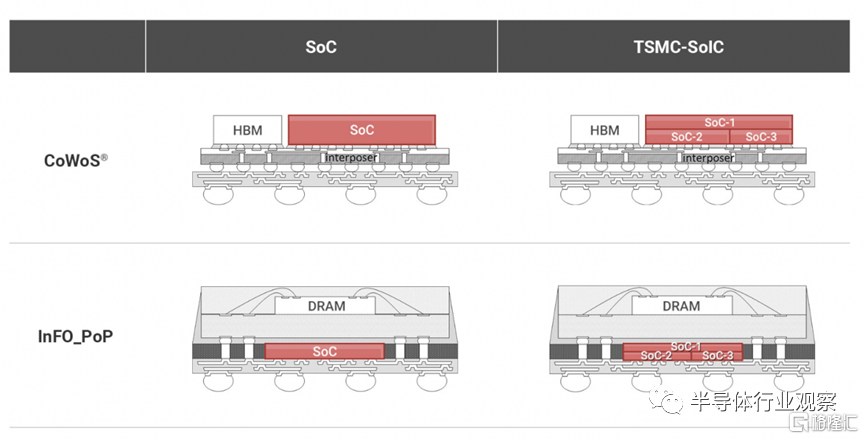

CoWoS(Chip On Wafer On Substrate)是一種2.5D的整合生產技術,由CoW和oS組合而來:先將芯片通過Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把CoW芯片與基板(Substrate)連接,整合成CoWoS。據悉,這也是蔣尚義在2006年提出的構想。

台積電CoWoS結構示意圖

CoWoS的核心是將不同的芯片堆疊在同一片硅中介層實現多顆芯片互聯。在硅中介層中,台積電使用微凸塊(μBmps)、硅穿孔(TSV)等技術,代替了傳統引线鍵合用於裸片間連接,大大提高了互聯密度以及數據傳輸帶寬。

CoWoS技術實現了提高系統性能、降低功耗、縮小封裝尺寸的目標,從而也使台積電在後續的封裝技術保持領先,爲超越摩爾定律奠定了堅實基礎。

然而,CoWoS剛推出時一度處境尷尬。由於價格昂貴,台積電CoWoS封裝只得到了FPGA大廠賽靈思的訂單,憑借CoWoS以及共同开發的TSV、μBump及RDL等技術,成功將4個28nm FPGA芯片拼接在一起,率先推出了史上最大的異構3D IC Virtex-7 HT系列FPGA芯片,從而帶來明顯的芯片尺寸縮小以及功耗和性能的優勢。

雖然CoWoS能夠爲芯片成品帶來優勢,但受限於成本,在推出的早期只有少數廠家的高端產品採用,賽靈思的項目是台積電先進封裝項目組在2012年收到的唯一訂單。對此,台積電決定給CoWoS做“減法”,开發出了廉價版的CoWoS技術,即InFO技術。

CoWoS技術之所以費錢,主要是由於在硅晶圓中間布线做連接。而InFO封裝把硅中介層換成了polyamide film材料,從而降低了單位成本和封裝高度。這兩項都是InFO技術在移動應用和HPC市場成功的重要標准。

因此,InFO技術一出現便廣受好評,當年蘋果的iPhone7、iPhone 7Plus處理器,採用的便是InFO封裝技術。這也成爲台積電後來能獨佔蘋果A系列處理器訂單的關鍵因素。

而實際上,真正引爆 CoWoS 的產品是AI芯片。2016 年,英偉達推出首款採用 CoWoS 封裝的GPU芯片GP100,爲全球AI熱潮拉开序幕;2017年Google、英特爾產品相繼交由台積電代工,採用CoWoS封裝。因成本高昂而坐冷板凳多年的CoWoS封測產能在2017年首度擴充。

除了CoWoS,台積電還有其他封裝技術。

2018年4月的美國加州聖塔克拉拉第二十四屆年度技術研討會上,台積電首度對外界公布了創新的系統整合單芯片(SoIC)多芯片3D堆疊技術。

據介紹,SoIC是一種創新的多芯片堆疊技術,是一種晶圓對晶圓的鍵合技術,SoIC是基於台積電的CoWoS與多晶圓堆疊(WoW)封裝技術开發的新一代創新封裝技術,這標志着台積電已具備直接爲客戶生產3D IC的能力。

根據台積電官方介紹,SoIC服務平台提供創新的前段3D芯片間堆疊技術,用於重新集成從片上系統(SoC)劃分的小芯片,最終的集成芯片在系統性能方面優於原始SoC,並且它還提供了集成其他系統功能的靈活性。相較2.5D封裝方案,SoIC的凸塊密度更高,傳輸速度更快,功耗更低。

台積電指出,SoIC服務平台可滿足雲,網絡和邊緣應用中不斷增長的計算,帶寬和延遲要求。它支持CoW和WoW方案,而這兩種方案在混合和匹配不同的芯片功能、尺寸和技術節點時提供了出色的設計靈活性。

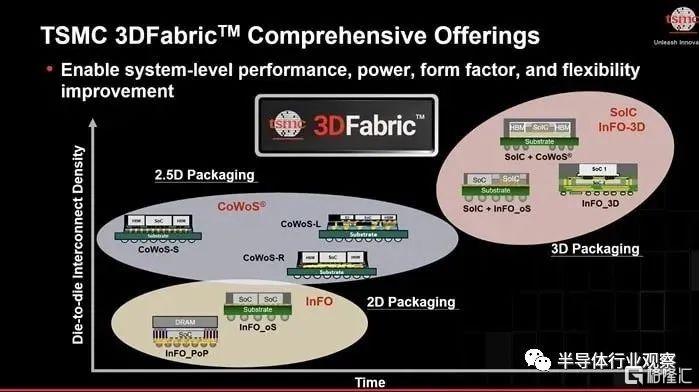

2020年,台積電宣布將其2.5D和3D封裝產品合並爲一個全面的品牌3DFabric,進一步將制程工藝和封裝技術深度整合,以加強競爭力。

3DFabric平台由SoIC(系統整合芯片)、InFO(整合型扇出封裝技術)、CoWoS(基板上芯片封裝)所組成,提供業界最完整且最多用途的解決方案,用於整合邏輯小芯片技術(Chiplet)、HBM、特殊制程芯片,實現更多創新產品設計。

作爲3D Fabric的一部分,台積電根據不同的中介層(interposer),把“CoWoS”封裝技術分爲三種類型:

CoWoS_S:它使用Si襯底作爲中介層。該類型是2011年开發的第一個“CoWoS”技術,在過去,“CoWoS”是指以硅基板作爲中介層的先進封裝技術;

CoWoS_R:它使用重新布线層(RDL)作爲中介層;

CoWoS_L:它使用小芯片(Chiplet)和RDL作爲中介層,結合了CoWoS-S和InFO技術的優點,具有靈活的集成性。

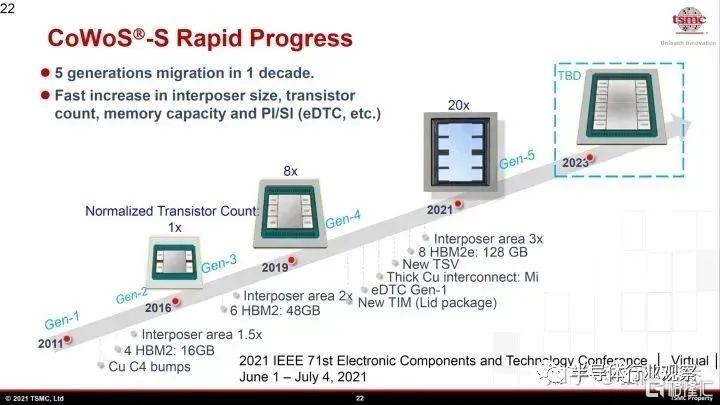

台積電通過早期的技術積累和大量成功案例,CoWoS封裝技術目前已迭代到了第5代。

CoWoS 封裝技術的路线圖

從2011年的第一代到2019年的第四代,CoWoS_S技術不斷擴大中介層面積、晶體管數量和內存容量。據悉,下一代(第6代)“CoWoS_S”計劃於2023年开發。Si中介層的尺寸更大,有四個掩模版。相應的HBM規範似乎是“HBM3”。

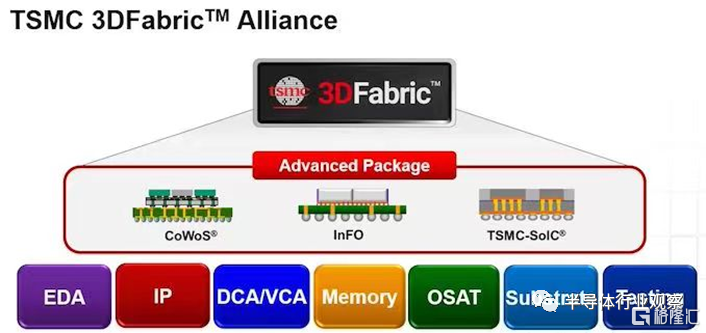

台積電還在去年11月宣布組建了一個先進封裝生態系統“3DFabric聯盟”, 包含EDA、IP、DCA/VCA、內存、OSAT、基板、測試7個環節頭部企業,旨在將其自有的封裝技術標准化,以便提前搶佔未來市場的主導地位。

台積電3D Fabric聯盟

(圖源:台積電)

英偉達、AMD、AWS等半導體設計公司正在使用3DFabric聯盟,隨着2.5D和3D封裝的使用吸引了更多的產品創意,合作夥伴的數量會隨着時間的推移而增加,3D芯片設計也將得到3DFabric聯盟中聚集的團隊合作的支持。

當前AI芯片訂單對台積電的貢獻度雖然不高,但市場需求卻持續提升,其中除了來自英偉達、AMD、博通、思科等IC設計大廠的訂單之外,雲端服務供應商如AWS、Google等也都相繼宣布將投入AI芯片的發展,讓目前幾乎囊括市場中所有人工智能制造芯片訂單的台積電相關產能供不應求。

隨着AI需求全面引爆,台積電啓動CoWoS大擴產計劃,業內傳出,台積電6月底再度向台系設備廠大舉追單,同時也要求供應商全力縮短交期支持,推估今年底CoWoS月產能將達到1.2萬片,2024年將翻倍成長。

台積電進軍封測領域的其中一個原因,也是希望能延伸自己的先進制程技術,通過制造高階CPU、GPU、FPGA芯片,並提供相應的封測流程,提供完整的“制造+封測”解決方案。

目前,在先進封裝領域,台積電的領先地位尤其突顯。據了解,台積電在先進封裝上已取得了可觀的收入體量,技術布局也進入關鍵節點,未來投入規模將持續加碼。根據Yole數據,2020-2022年,台積電在先進封裝上的營收規模從36億美元增至53億美元,年復合增長率爲21.3%;在先進封裝上的資本开支從15億美元增至40億美元,年復合增長率爲63.3%。從市場份額來看,2022年台積電在先進封裝上的營收規模和資本支出分別位列全球第三和第二。

可見,在先進封裝以及先進制程中,台積電時刻保持“兩手抓”的狀態,以確保自己在晶圓代工的霸主地位上,穩坐泰山。

英特爾緊追不舍

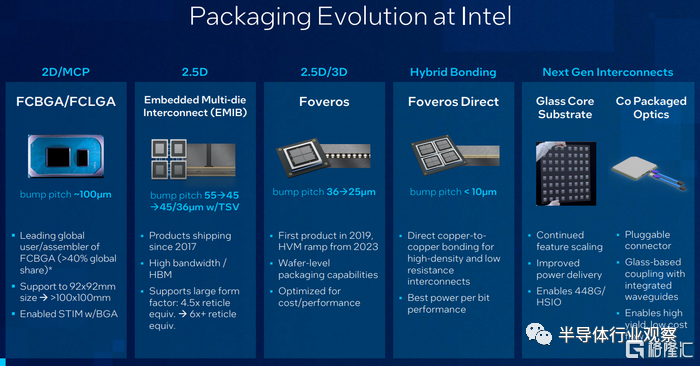

作爲IDM和晶圓代工大廠,英特爾也在積極布局2.5D/3D封裝。

通過多年技術探索,相繼推出了EMIB、Foveros和Co-EMIB等多種先進封裝技術,力圖通過2.5D、3D和埋入式等多種異構集成形式實現互連帶寬倍增與功耗減半的目標。

EMIB是英特爾在2.5D IC上的嘗試,其全稱是“Embedded Multi-Die Interconnect Bridge”。因爲沒有引入額外的硅中介層,而是只在兩枚裸片邊緣連接處加入了一條硅橋接層(Silicon Bridge),並重新定制化裸片邊緣的I/O引腳以配合橋接標准。

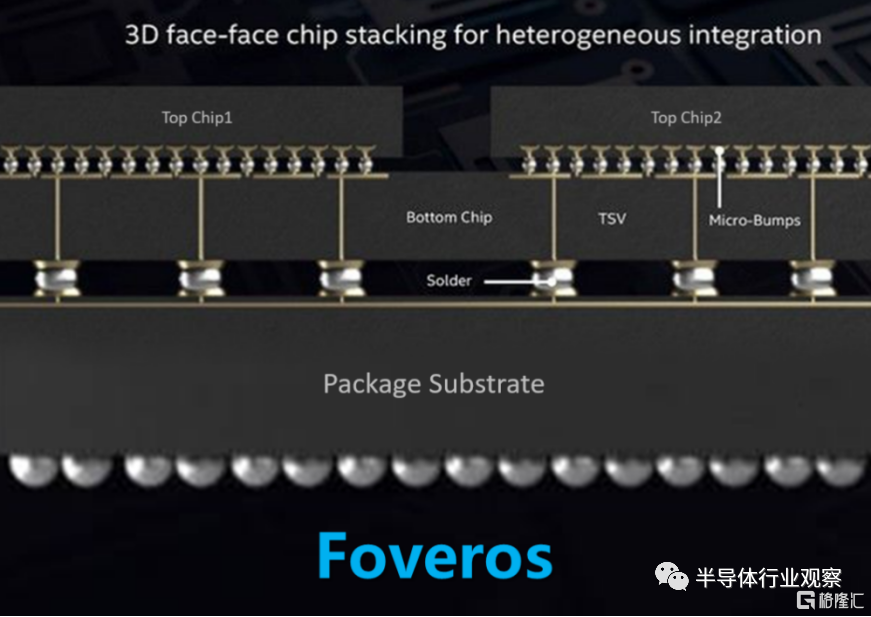

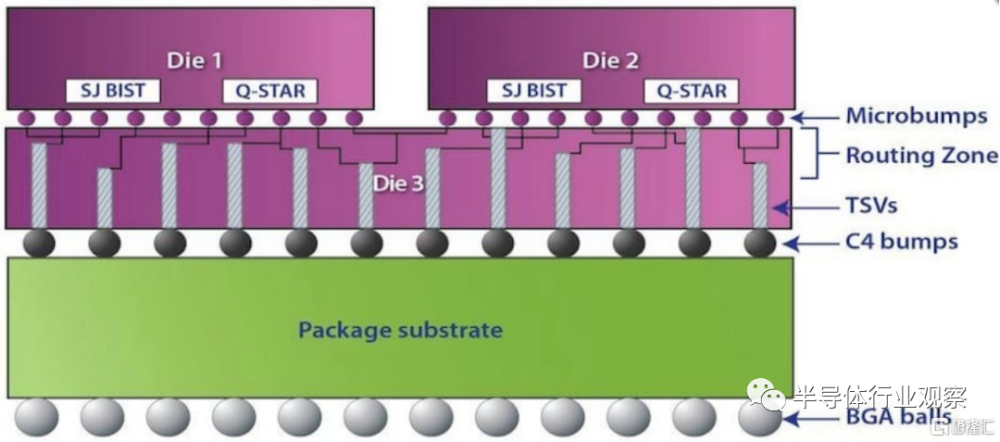

2018年12月,英特爾展示了名爲“Foveros”的全新3D封裝技術,這是繼2018年英特爾推出突破性的EMIB封裝技術之後,英特爾在先進封裝技術上的又一個飛躍。

據介紹,Foveros技術是英特爾首次引入3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片,進行橫向和縱向之間的互連,凸點間距進一步降低爲50-25um。Foveros爲整合高性能、高密度和低功耗硅工藝技術的器件和系統鋪平了道路。

英特爾表示,Foveros可以將不同工藝、結構、用途的芯片整合到一起,從而將更多的計算電路組裝到單個芯片上,實現高性能、高密度和低功耗。該技術提供了極大的靈活性,設計人員可以在新的產品形態中“混搭”不同的技術專利模塊、各種存儲芯片、I/O配置,並使得產品能夠分解成更小的“芯片組合”。

在2019年召开的SEMICON West大會上,英特爾再次推出了一項新的封裝技術Co-EMIB,這是一個將EMIB和Foveros技術相結合的創新應用。它能夠讓兩個或多個Foveros元件互連,並且基本達到單芯片的性能水准。設計人員也能夠利用Co-EMIB技術實現高帶寬和低功耗的連接模擬器、內存和其他模塊。

英特爾在其2020年架構日中,展示了其在3D封裝技術領域中的新進展,英特爾稱其爲“混合鍵合(Hybrid bonding)”技術。

當今大多數封裝技術中使用的是傳統的“熱壓鍵合”技術,混合鍵合是這一技術的替代品。這項新技術能夠加速實現10微米及以下的凸點間距,提供更高的互連密度、帶寬和更低的功率。

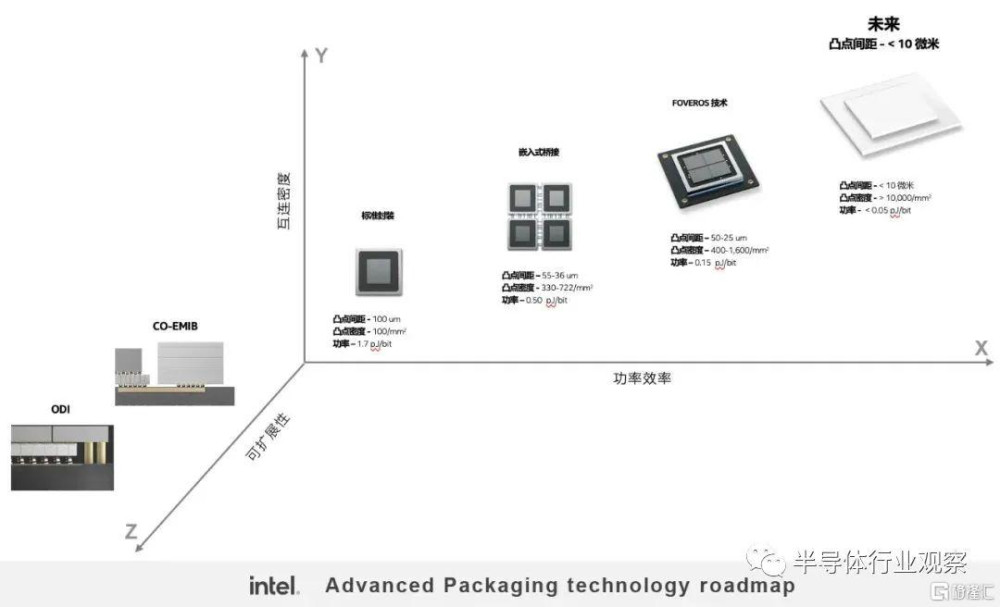

英特爾先進封裝技術路线圖

從英特爾的先進封裝技術發展路线圖能看到,其先進封裝主要關注互連密度、功率效率和可擴展性三個方面。其中,Foveros和混合鍵合技術主要關注功率效率、互連密度方面,而Co-emib和ODI技術則體現了集成的可擴展性特點。從Foveros到混合鍵合技術,英特爾逐漸實現凸點間距越來越小,使系統擁有更高的電流負載能力、更好的熱性能。未來英特爾將繼續致力於實現每毫米立方體裏功能最大。

今年5月,英特爾發布了先進封裝技術藍圖,計劃將傳統基板轉爲更爲先進的玻璃材質基板。

英特爾先進封裝技術藍圖

報道稱,英特爾此舉是對材料進行轉換以實現超越現有塑料基板限制的高性能半導體的嘗試。

隨着3D封裝的普及,厚度是一個更受關注的因素。通過垂直堆疊半導體來提高性能,其關鍵是減小基板的厚度。玻璃載板具有平坦的表面並且可以做得很薄,與ABF塑料相比,其厚度可以減少一半左右,減薄可以提高信號傳輸速度和功率效率。

因此,英特爾有望通過玻璃載板改進3D封裝結構。

此外,英特爾還在推進一項技術,該技術可縮短芯片與電路板之間的接觸距離(凸點間距)。接觸距離越短,封裝尺寸越小,因此可以提高性能。英特爾現在已經實現了大約36μm)的凸點間距,英特爾表示計劃明年將其減少到25μm。

從上圖還能看到,英特爾也在开發一個名爲Intel Foveros Direct的混合鍵合技術。到目前爲止,在堆疊半導體或將它們連接到電路板時一直使用焊球。混合鍵合則是將具有優良電性能的銅和銅直接連接起來,以減少堆疊間隙,提高信號傳輸速度。英特爾預測混合鍵合會將凸點間距減小到10μm以下,最快從今年下半年开始應用到英特爾的制造工藝中。

另外,隨着ChatGPT引發的計算需求暴漲,硅光模塊中的CPO(共封裝光學)技術作爲優化算力成本的關鍵技術,發展潛力巨大。英特爾也正在布局於此。

共封裝光子是業界公認未來高速率產品形態,是未來解決高速光電子的熱和功耗問題的最優解決方案之一,有望成爲產業競爭的主要着力點。

據了解,CPO是一種新型的光電子集成技術,它將激光器、調制器、光接收器等光學器件封裝在芯片級別上,直接與芯片內的電路相集成,借助光互連以提高通信系統的性能和功率效率。

與傳統的光模塊相比,CPO在相同數據傳輸速率下可以減少約50%的功耗,將有效解決高速高密度互連傳輸場景下,電互連受能耗限制難以大幅提升數據傳輸能力的問題。與此同時,相較傳統以III-V材料爲基礎的光技術,CPO主要採用的硅光技術具備成本、尺寸等優勢。

過去很長時間內,英特爾的封裝技術主要用在自家產品上,對市場造成的影響較小。而隨着英特爾提出IDM 2.0發展策略,晶圓代工業務成爲英特爾重要轉型項目,除了爲高通等無廠半導體企業代工制造以外,其封裝技術也是英特爾極力推銷的對象。英特爾表示,客戶可選擇由台積電、GF等進行代工,之後利用英特爾技術進行封裝、測試,這一模式將爲客戶帶來更靈活的產品制造方式。

英特爾強調,目前已經與全球前10大芯片封裝廠旗下客戶進行洽談,並且獲得Cisco、AWS在內業者青睞。

三星略顯遲緩

雖然三星去年領先台積電率先量產3納米芯片,但台積電無可匹敵的封裝技術說明了,爲何全球科技巨擘仍然倚重台積電。當前,AI和自動駕駛芯片大單全誒台積電喫下,三星與台積電的市佔差距正越來越大。

面向AI時代的機遇,三星自然不會拱手相讓。

在6月底召开的三星晶圓代工論壇上,三星代工業務負責人Siyoung Choi先是透露面向高性能計算需求的2nm工藝將在2026年量產。隨後又宣布與內存、基板封裝、測試等領域的合作夥伴成立“MDI(多芯片集成)聯盟”,構建2.5D和3D異構集成的封裝技術生態,基於聯盟和生態合作,三星將爲下遊客戶提供一站式服務,並通過定制化的封裝方案开發,滿足高性能計算和汽車等領域的需求。

在此之前,三星已經推出了I-Cube、X-Cube等2.5D和3D封裝技術,此次成立聯盟將提升其產業鏈整合能力,以及一站式和定制化服務能力。

針對2.5D封裝,三星推出的I-Cube封裝制程可與台積電CoWoS封裝制程相抗衡;3D IC技術方面,三星2020年推出X-Cube封裝,將硅晶圓或芯片物理堆疊在一起,每個晶圓都通過硅通孔(TSV)連接,最大程度上縮短互連長度,在降低功耗的同時能提高傳輸速率。

從產品上看,三星表示已經通過X-Cube封裝技術將4顆SRAM堆疊在邏輯核心運算芯片上,並使用TSV技術進行連接,X-Cube封裝技術已應用於7nm EUV制程,並在次世代5nm制程進行驗證,未來將鎖定HPC、5G、AI等應用領域。

此外,三星計劃在2024年量產可處理比普通凸塊更多數據的X-Cube(u-Bump)封裝技術,並預計2026年推出比X-Cube(u-Bump)處理更多數據的無凸塊型封裝技術。據悉,2021年,三星還對外宣稱正在开發“3.5D封裝”技術,目前還未有最新消息。

在2023年度“三星晶圓代工論壇”上,三星電子代工業務總裁崔世英還介紹了三星的晶圓代工路线策略。崔世英表示,三星計劃到2025年將GAA制程技術制造的芯片應用擴展到3D封裝上,原因是制程微縮在降低成本和縮小芯片面積方面存在限制,因此三星正在多樣化其後段先進技術。

當前業界尚未將GAA制程技術與3D先進封裝技術互相結合,主要是因爲這兩種制程技術的復雜度都很高。其中,GAA制程技術取代了傳統的FinFET制程技術,最大化了數據傳輸路徑的面積,同時減小了芯片的尺寸。至於3D先進封裝則是一種整合技術,可以使不同的小芯片堆疊在一起,並在一個封裝內,可以像單個芯片一樣發揮作用。

這些技術在當前制程微縮逐步達到極限的情況下,顯得尤爲重要。目前,英特爾和台積電等競爭對手都正在先進封裝領域激烈競爭,以增強這些技術的商用化。

相比台積電和英特爾,盡管三星電子的先進封裝投資稍顯遲緩,但這兩年在先進封裝上的押注也非常大。

前些年三星推出了扇出型面板級封裝(Fan-Out Panel Level Package, FOPLP)技術,在大面積的扇出型封裝上進一步降低封裝體的剖面高度、增強互連帶寬、壓縮單位面積成本,目的是取得更高的性價比。

三星的先進封裝技術相對台積電起步較晚,三星原本想以扇出型面板級封裝(FOPLP)技術搶奪手機AP市場份額,然而,三星一直未能很好地解決FOPLP的翹曲等問題。同時,FOPLP封裝的芯片精度無法與晶圓級封裝相比,使得良率和成本難題無法得到改善。目前採用FOPLP量產的芯片仍然以智能穿戴設備應用爲主,還無法在智能手機等要求更高的應用實現規模量產。

自今年年初以來,三星一直在投資其Cheonan封裝生產线。

另據業內人士透露,三星還在加緊布局FO,並計劃投資7500萬美元在日本建立相關產线,並在尋求加強與日本芯片制造設備和材料供應商的聯系,在FO領域,目前台積電獨大,大約佔據77%的市場份額,三星有意來分一杯羹。按照三星先前公布的計劃,其目標是在2027年將先進制程產能較2022年提升3倍以上。

三星在先進封裝技術上的優勢

(圖源:三星)

除了在產品創新上的投入和布局之外,三星電子去年开始還積極推進封裝基礎設施建設和人才引進。2022年12月,三星電子成立了先進封裝(AVP)部門,負責封裝技術和產品开發,目標是用先進的封裝技術超越半導體的極限。

三星AVP業務副總裁暨團隊負責人Kang Moon-soo近日指出,三星電子是世界上唯一一家從事存儲器、邏輯芯片代工和封裝業務的公司。因此,利用這些優勢,三星將提供具有競爭力的封裝產品,連接高性能存儲器,例如通過異質整合技術,並經由EUV制造技術生產最先進的邏輯半導體和HBM。

“未來,三星將專注於开發基於再分布層(RDL)、硅中介層/橋和硅通孔(TSV)堆疊技術的下一代2.5D和3D先進封裝解決方案。” Kang Moon-soo進一步強調道。

爲實現先進封裝領域的突破和追趕,今年3月,三星電子聘請了曾在台積電工作了近19年的資深工程師林俊成擔任半導體(DS)部門先進封裝業務團隊(AVP)副社長,林俊成預計今後將在該部門开展先進封裝技術的开發工作。

林俊成從1999年至2017年任職於台積電,被稱爲“半導體封裝專家”。在此期間,他申請美國專利450多項,爲台積電當前引以爲傲的3D封裝技術奠定了基礎。

在聘請林俊成之前,三星電子還挖來了蘋果出身的副社長金宇平,並將其任命爲美國封裝解決方案中心負責人。

在先進封裝技術的大力布局,加上在3nm和2nm先進制程領域量產時間的激進安排,三星正在加強與與台積電在AI芯片大單方面的角逐。無論三星能否挑战台積電在AI時代的領先地位,只要有角逐的意識和動作,就能通過更加充分的競爭逐步提升晶圓級封裝的性價比,讓芯片設計企業有更多的選擇。

聯電快速跟進

6月26日,晶圓代工廠聯電發布公告稱,將以新台幣3.85億元向西門子EDA取得研發生產軟件。預計這將提供聯電在晶圓堆疊(WoW)和芯片晶圓堆疊(CoW)技術提供的3D IC規劃及組裝驗證方案。

換句話說,聯電將具備2.5D、3D IC與扇出型晶圓級封裝能力,以滿足客戶先進封裝的需求。

在此之前,聯電布局先進封裝領域也有跡可循。今年年初,聯電宣布攜手Cadence共同开發3D IC混合鍵合(Hybrid Bond)解決方案,該方案聯電也已准備就緒,整合跨制程的技術,支持邊緣AI、圖像處理和無线通訊等終端應用的开發。

聯電客戶對於高性能運算、射頻和AIoT等應用需求日益提升,3D IC需求相應增長,與全球EDA廠合作,能夠協助客戶加快整合產品設計之上市時間。聯電以其豐富的晶圓凸塊、堆疊式芯片及晶圓級封裝等一站式服務經驗,拓展至2.5D、3D IC解決方案,力求卡位先進封裝商機。

格芯換道布局

2019年,格芯(GlobalFoundries)宣布採用12nm FinFET工藝,成功流片了基於ARM架構的高性能3D封裝芯片,意味着格芯亦投身於3D封裝領域。

格芯在2018年宣布放棄繼續在7nm以及更加先進的制造工藝方向的研發,但這並不意味着在其它新技術上再也無所作爲。

此次在3D封裝技術上的發力,正是格芯在大趨勢下所做出的努力,其新开發的3D封裝解決方案不僅可爲IC設計公司提供異構邏輯和邏輯/內存集成途徑,還可以優化生產節點制造,從而實現更低延遲、更高帶寬和更小特徵尺寸,意味着將與英特爾、台積電等公司一道競爭異構計算時代的技術主動權。

格芯首席技術專家John Pellerin表示:“在大數據與認知計算時代,先進封裝的作用遠甚以往。AI的使用與高吞吐量節能互連的需求,正通過先進封裝技術推動加速器的增長。”

今年早些時候,格芯官網發布公告,宣布與美國最大的半導體封裝和測試服務提供商安靠科技結成战略合作夥伴關系。格芯計劃將其德累斯頓工廠的12英寸晶圓級封裝產线轉移到安靠位於葡萄牙波爾圖的工廠,以在歐洲建立第一個大規模後道設施。

公告稱,目前安靠擁有歐洲唯一一家大型OSAT設施,而格芯是歐洲最大、最先進的半導體制造服務公司。該合作夥伴關系通過亞洲以外的先進封裝半導體供應鏈,爲包括汽車在內的關鍵終端市場創造了更多的歐洲供應鏈自主權。

安靠業務部門執行副總裁Kevin Engel表示:"與格芯的战略合作將加強歐洲的先進半導體封裝供應鏈,提高競爭能力,以補充亞洲的現有能力。Amkor與格芯的合作使我們能夠顯著擴大生產規模,並爲市場帶來更多的裝配和測試能力,以支持我們的歐洲和全球客戶。"

中芯國際攜手長電

中芯國際也看到了先進封裝的前景。

早在2014年,中芯國際就與長電科技合資成立中芯長電,是全球首家採用集成電路前段芯片制造體系和標准,採用獨立專業代工模式服務全球客戶的中段硅片制造企業。

中芯長電以先進的凸塊和再布线加工起步,致力於提供中段硅片制造和測試服務,並進一步發展先進的三維系統集成芯片業務。

據了解,目前中芯長電位於江陰的基地提供12英寸中段硅片加工,專注於12英寸凸塊和先進硅片級封裝;上海基地提供8英寸中段凸塊和硅片級封裝。另外在江陰以及上海兩地均擁有測試廠,能夠提供測試程序开發、探針卡制作、晶圓測試、失效分析以及失效測試服務。

寫在最後

隨着運算需求的日益復雜,異構計算大行其道,更多不同類型的芯片需要被集成在一起,而依靠縮小线寬的辦法已經無法同時滿足性能、功耗、面積以及信號傳輸速度等多方面的要求。

在此情況下,越來越多的半導體廠商开始把注意力放在系統集成層面。除了傳統委外封測廠商(OSAT)之外,近年來晶圓代工廠、IDM也在大力發展先進封裝或相關技術,甚至有Fabless和OEM也參與其中,通過封裝技術尋求解決方案。

不同商業模式的企業都在同一個高端封裝市場空間展开競爭。但是不同業態的廠商,在封裝業務方面投入的資源也有所不同,技術發展路线也存在差異。

Foundry方面,由於2.5D/3D封裝技術中涉及前道工序的延續,晶圓代工廠對前道制程非常了解,對整體布线的架構有更深刻的理解,走的是芯片制造+封裝高度融合的路线。因此,在高密度的先進封裝方面,Foundry比傳統OSAT廠更具優勢。

這也使得先進封裝成爲當前業內幾大主流半導體晶圓制造廠商重點發展的技術。台積電、英特爾和三星等代工巨頭已成功利用先進封裝市場的增長,實現了其技術壁壘的不斷提升。

後摩爾時代,先進封裝正在成爲各大廠商的發力點和必然選擇,除了原有的IDM封測部、OSAT外包封測企業外,半導體制造龍頭企業也已從過去晶圓制造技術節點的推進,轉向先進封裝技術的創新。

台積電、英特爾、三星等頭部玩家都不約而同拿出殺手鐗來競爭行業地位,晶圓代工廠正在成爲此輪技術革新中的最大攪局者。

標題:代工巨頭“血拼”先進封裝

地址:https://www.iknowplus.com/post/15076.html